# **Display Specification for**

# 13.3" Wide (1280x800) TFT-LCD

# With LED Backlight

# **Revision History**

| DATE      | <u>REV #</u> | Section # | CHANGE DESCRIPTION |

|-----------|--------------|-----------|--------------------|

| 8/15/2008 | А            | All       | Release            |

|           |              |           |                    |

|           |              |           |                    |

|           |              |           |                    |

|           |              |           |                    |

|           |              |           |                    |

# **Table of Content**

| Revision History                                                | 2  |

|-----------------------------------------------------------------|----|

| 1. General Description                                          | 7  |

| 2. ORDER OF PRECEDENCE OF DOCUMENTATION AUTHORITY               | 8  |

| 2.1. The Purchase Order                                         | 8  |

| 2.2. This Specification                                         | 8  |

| 2.3. Reference Documents                                        | 8  |

| 3. PHYSICAL DESCRIPTION                                         | 9  |

| 4. MECHANICAL REQUIREMENTS                                      | 10 |

| 5. ELECTRICAL REQUIREMENTS                                      | 12 |

| 5.1. Block Diagram                                              | 12 |

| 5.2. Display PCB Schematics                                     | 13 |

| 5.3. Display PCB Layout                                         | 14 |

| 5.4. Display Subsystem (PCB & TFT Panel)                        | 15 |

| 5.4.1. Pin-Out (Single Channel LVDS Interface)                  | 15 |

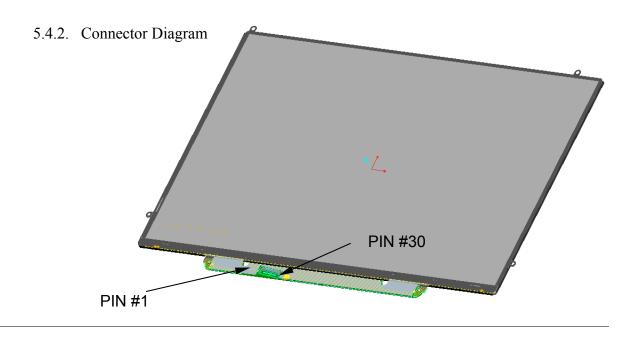

| 5.4.2. Connector Diagram                                        | 16 |

| 5.4.3. Color Input Data Reference                               | 17 |

| 5.4.4. EDID Interface (Per Vesa EDID 1.x standard requirements) | 19 |

| 5.4.5. Electrical Ratings                                       | 22 |

| 5.4.6. Signal Timing                                            | 24 |

| 5.4.6.1. Signal Impedance                                       | 24 |

| 5.4.6.2. Timing Data                                            | 24 |

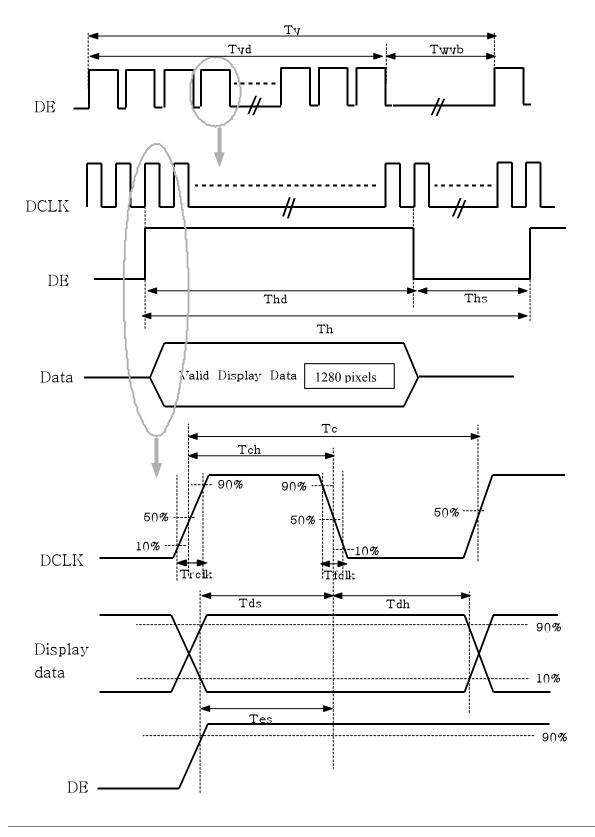

| 5.4.6.3. Video Timing Diagram                                   | 26 |

| 5.4.7. Power Measurements (W/O backlight)                       | 27 |

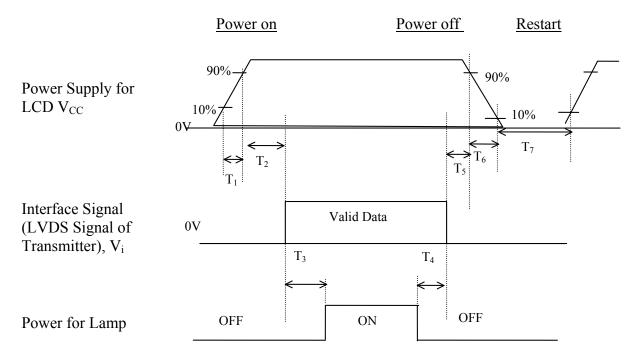

| 5.4.8. Power on-off sequence                                    | 28 |

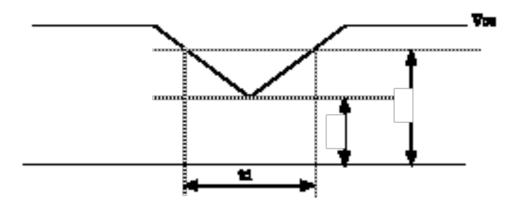

| 5.4.9. Vcc Dip Condition                                        | 29 |

| 5.5. Near-Field Noise                                           | 29 |

| 5.6. Backlight Subsystem                                        | 29 |

| 6. OPTICAL REQUIREMENTS                                         | 32 |

| <b>LG.PHILIPS</b> LCD | PHILIPS<br>+<br>+ |

|-----------------------|-------------------|

|-----------------------|-------------------|

| 6.1. Optical Specifications                                                             | 32       |

|-----------------------------------------------------------------------------------------|----------|

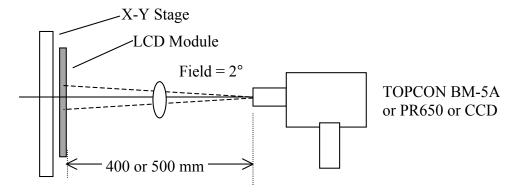

| 6.2. Measuring Conditions                                                               | 33       |

| 6.3. Definition                                                                         | 35       |

| 6.3.1. Center Point Luminance                                                           | 35       |

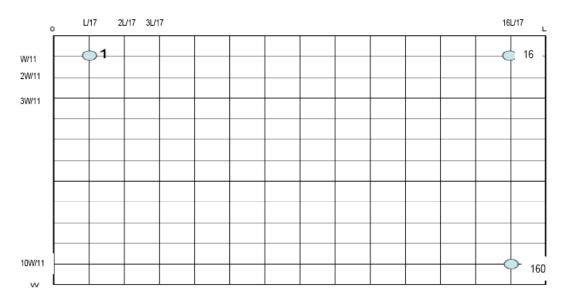

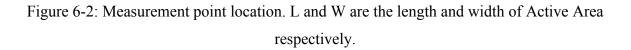

| 6.3.2. Average Luminance                                                                | 35       |

| 6.3.3. Luminance Uniformity                                                             | 35       |

| 6.3.3.1. Global Luminance Uniformity:                                                   | 36       |

| 6.3.3.2. Worst Neighbor Luminance Uniformity (The 4 points that are closest to the test |          |

| $\frac{36}{36}$                                                                         | n poini) |

| 6.3.4. Contrast Ratio                                                                   | 36       |

| 6.3.5. White Color Uniformity                                                           | 36       |

| 6.3.5.1. Panel to Panel White Color Uniformity                                          | 37       |

| 6.3.5.2. Max Color Difference with respect to the center within a panel                 | 37       |

| 6.3.5.3. Max Color Difference between any two points within the panel                   | 37       |

| 6.3.5.4. Max Color Difference between two neighbors                                     | 37       |

| 6.3.6. RGB Color Chromaticity                                                           | 37       |

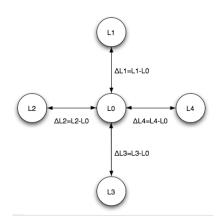

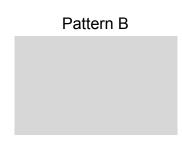

| 6.3.7. Viewing Angle                                                                    | 37       |

| 6.3.8. Gray Scale Inversion                                                             | 38       |

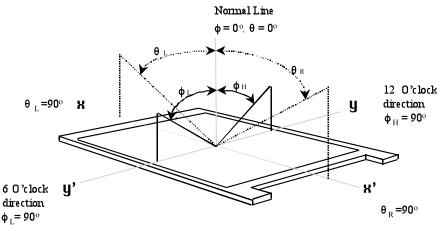

| 6.3.9. Response Time                                                                    | 38       |

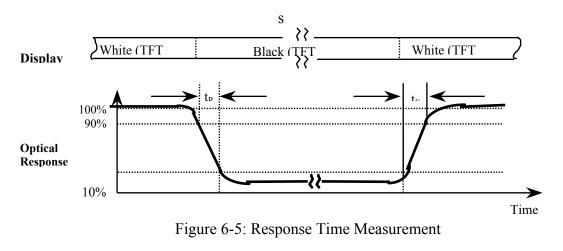

| 6.3.9.1. On and Off Response Time                                                       | 38       |

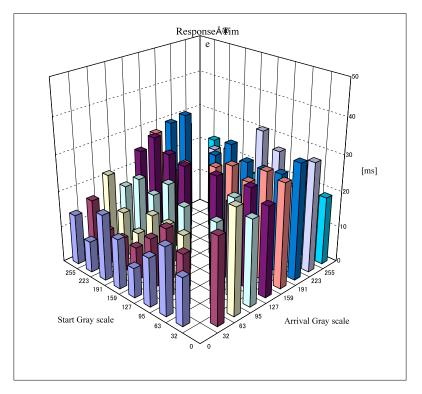

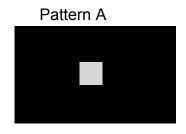

| 6.3.9.2. Gray to Gray Response Time                                                     | 39       |

| 6.3.10. Gray Scale Linearity or Gamma Value                                             | 39       |

| 6.3.11. Flicker                                                                         | 40       |

| 6.3.12. Cross-talk                                                                      | 40       |

| 6.4. Hot Spot Specifications:                                                           | 40       |

| 6.5. FOS Shimmering Specifications                                                      | 41       |

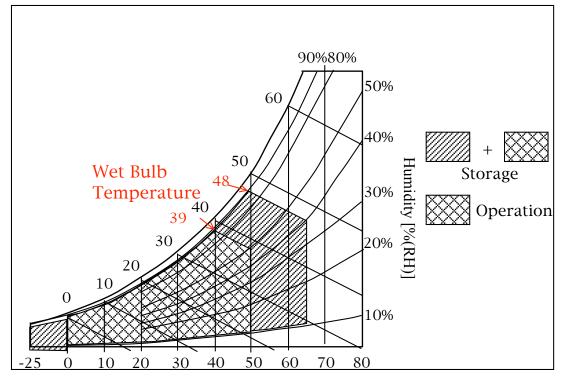

| 7. ENVIRONMENTAL                                                                        | 42       |

| 7.1. Shock and Vibration                                                                | 42       |

| 7.2. Temperature and Humidity                                                           | 44       |

| 7.2.1. General Performance Requirements                                                 | 45       |

| 7.2.2. Non-operational Testing                                                          | 46       |

| 7.2.2.1. Low Temperature                                                                | 46       |

|                                                                                         |          |

| 7.2.2.2. High Temperature                                           | 46 |

|---------------------------------------------------------------------|----|

| 7.2.2.3. High Temperature and High Humidity                         | 46 |

| 7.2.2.4. Thermal Shock                                              | 46 |

| 7.2.3. Operational Testing                                          | 46 |

| 7.2.3.1. Low Temperature                                            | 46 |

| 7.2.3.2. High Temperature                                           | 46 |

| 7.2.3.3. High Temperature and High Humidity                         | 46 |

| 7.2.3.4. Four Corner Test (72 hrs – operating)                      | 46 |

| 7.3. Altitude                                                       | 47 |

| 8. RELIABILITY                                                      | 47 |

| 8.1. Resistance to Normal Abuse                                     | 47 |

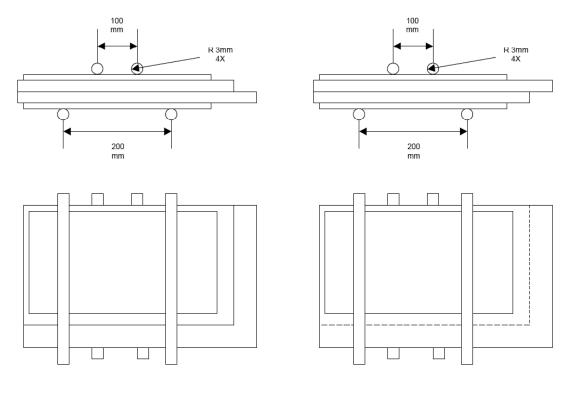

| 8.1.1. Torsion Test                                                 | 47 |

| 8.1.2. Test Conditions:                                             | 47 |

| 8.1.3. Test Set-up                                                  | 48 |

| 8.1.4. Static Load Deflection and Breakage                          | 48 |

| 8.2. Electrostatic Discharge (ESD)                                  | 48 |

| 8.3. MTBF                                                           | 48 |

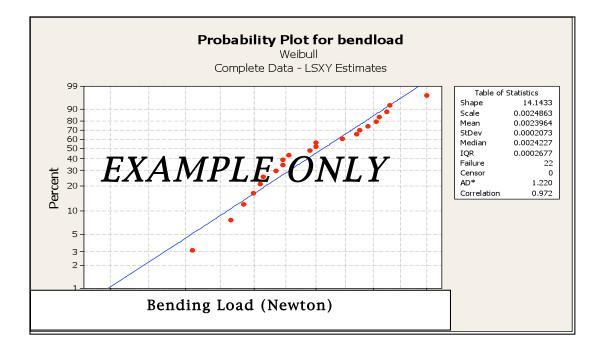

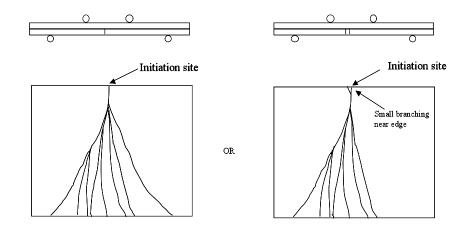

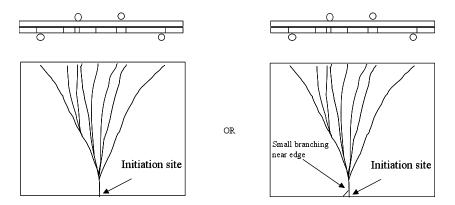

| 8.4. LCD Glass Strength                                             | 49 |

| 8.5. Itemized On-going Reliability Test Requirements                | 54 |

| 8.5.1. Environmental Test                                           | 54 |

| 8.5.2. Component FAI Measurement                                    | 55 |

| 8.5.3. Optical Test                                                 | 55 |

| 8.5.4. Electrical Test                                              | 55 |

| 9. COSMETIC REQUIREMENTS                                            | 57 |

| 10. REGULATORY                                                      | 58 |

| 10.1. Product Safety (Environmental, Ergonomics, Safety and Health) | 58 |

| 10.2. RoHS Compliance and other Substance Regulations               | 58 |

| 10.3 Halogen Free                                                   | 58 |

| 10.3. Environmental Markings and Recycling                          | 59 |

| 10.4. Product Safety                                                | 59 |

| 10.5. Ergonomics                                                    | 59 |

| 10. | 6. Electromagnetic Compatibility (EMC) | 59 |

|-----|----------------------------------------|----|

| 11  | FACTORY/SERVICE REQUIREMENTS           | 61 |

| 12  | REFERENCE DOCUMENTS                    | 62 |

# 1. General Description

This document establishes the requirements for the display device for the M97 project.

| CategoryParameterSpecification              |                     | <u>Specification</u>                                     |  |  |

|---------------------------------------------|---------------------|----------------------------------------------------------|--|--|

| General                                     | Manufacturer        | LGD                                                      |  |  |

|                                             | Mfg. P/N            | LP133WX2-TLC1 (for Heesung backlight)                    |  |  |

|                                             |                     | LP133WX2-TLC1 (for Radiant backlight)                    |  |  |

|                                             | LCD TYPE            | Normally-White, Transmissive TN TFT-LCD                  |  |  |

|                                             | Diagonal            | 13.282" (33.74cm)                                        |  |  |

|                                             | Pixel Format        | 1280 (RGB stripe, H) x 800 (V)                           |  |  |

|                                             | Pixel Pitch         | 0.2235(V) x 3x0.0745(H) mm                               |  |  |

|                                             | Color Depth         | 18-bits (6R, 6G, 6B), 262144 colors                      |  |  |

|                                             | Pooling requirement | Rigid Post Spacer with strong pooling resistance         |  |  |

|                                             | Packaging           | Protective film on front polarizer. Displays packaged    |  |  |

|                                             |                     | and air-tight sealed in anti-static bags.                |  |  |

| Electrical                                  | Interface           | 3.3V single-channel LVDS                                 |  |  |

|                                             | Power Consumption   | 4.3 W @ Black (typical, the logic plus the backlight     |  |  |

|                                             |                     | @95% duty cycle @20mA, 3.3V forward bias voltage)        |  |  |

| OpticalLuminance275 nits @ 95% duty cycle @ |                     | 275 nits @ 95% duty cycle @20 mA (typical center)        |  |  |

|                                             | White LED Backlight | 6 strings, 9 LED per string.                             |  |  |

|                                             |                     | Nichia NNSW108T-S1, TG E1S62-YW1D7-08                    |  |  |

|                                             | Hot Spots           | No visible hot spot at any angle                         |  |  |

|                                             | Viewing Direction   | 6:00 for worst dark inversion (pcb driver on the bottom) |  |  |

| Contrast 500 typical                        |                     | 500 typical                                              |  |  |

| Top Polarizer     Glossy Su coating         |                     | Glossy Surface, 3H Hard Coating, LT4/ARC7 AR             |  |  |

|                                             |                     | coating                                                  |  |  |

|                                             | Diffuser Sheet      | Tsujiden D153GS (top) & Tsujiden D120 (Bottom)           |  |  |

|                                             | BEF Sheet           | 2 X BEF2-G2 MR (Halogen free)                            |  |  |

| LG.PHILIPS LCD |

|----------------|

|----------------|

|               | Reflector             | E6SR (sulfur free)                |

|---------------|-----------------------|-----------------------------------|

|               | LGP                   | РММА                              |

| Mechanical    | Active Area           | 286.08 mm (H) x 178.80 mm (V)     |

|               | Minimum Viewing Area  | 288.08 mm (H) x 180.80 mm (V)     |

|               | Module Outline Size   | 297.150 mm (H) x 192.150 mm (V)   |

|               | Connector             | IPEX 20474-030E-12                |

|               | Mating Connector      | IPEX 20472-030T-10                |

|               | Weight                | 300 grams typical                 |

| Environmental | Operating Temperature | $0^{\circ}C \sim +50^{\circ}C$    |

|               | Storage Temperature   | -25°C ~+65°C                      |

| Pre-Aging     | Before shipment       | Minimum 2 hours at 50°C, panel on |

## 2. ORDER OF PRECEDENCE OF DOCUMENTATION AUTHORITY

In the case of any conflict in any specification related to these parts, this order of precedence of authority shall apply:

- 2.1. The Purchase Order

- 2.2. This Specification

- 2.3. Reference Documents

### 3. PHYSICAL DESCRIPTION

3.1. Display Mode

Normally White, Transmissive, Twisted Nematic Liquid Crystal Displays

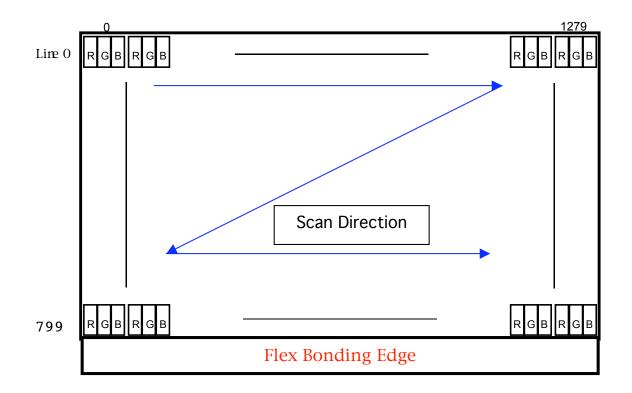

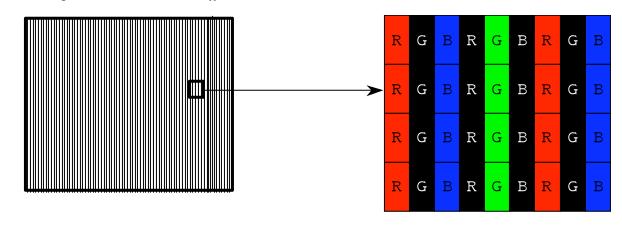

3.2. Pixel Configuration

**RGB** Vertical Stripe

3.3. Pixel Pitch

0.2235 mm x 0.2235 mm

3.4. Resolution

1280 (RGB stripe, H) x 800 (V)

3.5. Aperture Ratio

Minimum > TBD

3.6. Optimum Viewing Cone

6 o'clock worst dark inversion direction (PCB on the bottom)

3.7. Interface & Driving Scheme

3.3V single-channel LVDS (Flat Link) interface, requiring Hsync and Vsync signals, along with DE (Data Enable) mode, 2-dot inversion

3.8. Front Surface Treatment

$\label{eq:Low-reflection gloss surface, ~1\% Reflectance, \geq 3H hardness (Sumitomo LT4, or Nitto Denko ARC7)$

3.9 Environmental Requirements:

Any homogeneous component must meet Apple Halogen-Free Specification, 069-1857.

Display assembly shall not contain arsenic in the glass, in accordance with the Apple Regulated Substances Specification, 069-0135. Restrictions on arsenic are not applicable to semiconductor materials.

Display assembly shall not contain mercury, in accordance with the Apple Regulated Substances Specification, 069-0135.

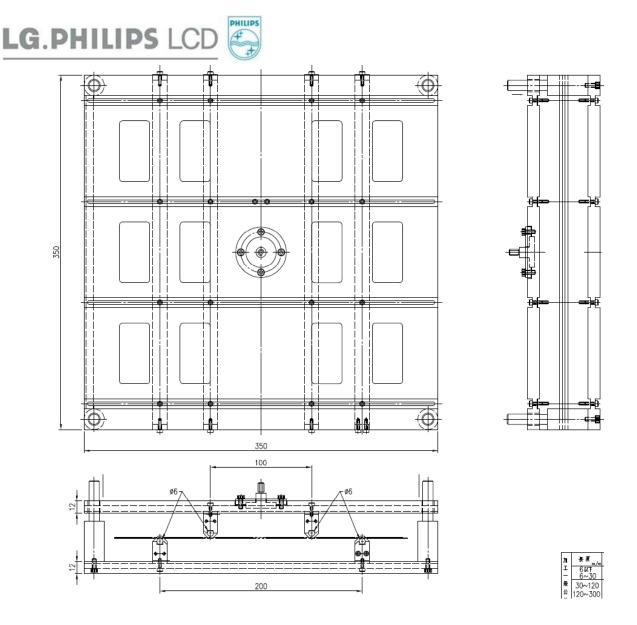

### 4. MECHANICAL REQUIREMENTS

### 4.1. Dimensions and Tolerances

Refer to Apple MCO 069-2659, which include height, width, and thickness, mounting details, bulb location, cable length, and connectors. The LCD module outline is described in the following table.

| Dimension      | Min    | Тур    | Max    | Unit |

|----------------|--------|--------|--------|------|

| Horizontal (H) | 296.85 | 297.15 | 297.45 | mm   |

| Vertical (V)   | 191.85 | 192.15 | 192.45 | mm   |

| Depth (D)      | 3.00   | 3.30   | 3.60   | mm   |

### 4.2. Weight

300 g (typical), 310 g (max)

4.3. Stack-up (tentative)

| Mechanical Stack-up          | Part #           | Thickness /mm |

|------------------------------|------------------|---------------|

| Top Polarizer                |                  |               |

| (glossy, LT4 or ARC7)        | LGC, 6308L-1543A | 0.215         |

| LCD Glass CF                 |                  | 0.5           |

| LCD Glass TFT                |                  | 0.5           |

| Bottom Polarizer             |                  | 0.135         |

| Total Design Gap             | -                | 0.135         |

| Upper Diffuser               | Tsujiden D153GS  | 0.095         |

| Upper BEF (Halogen Free)     | BEF II-GII MR    | 0.155         |

| Lower BEF (Halogen Free)     | BEF II-GII MR    | 0.155         |

| Lower Diffuser               | Tsujiden D120    | 0.12          |

| Light Guide                  | PMMA             | 0.72          |

| White Reflector (Sulfur-free |                  |               |

| reflector for PMMA           |                  |               |

| backlight)                   | E6SR             | 0.188         |

| Rear Bezel                   | SUS 304          | 0.3           |

| Таре                         |                  | 0.1           |

| Total Typical Thickness      | w/o PCB          | 3.30          |

| Maximum Tolerance            |                  | 0.3           |

| Total Maximum Thickness | (w/o PCB) | 3.60 |

|-------------------------|-----------|------|

| PCB Thickness (8 Layer  |           |      |

| PCB)                    |           | 0.8  |

| Maximum Component - 1   |           |      |

| side (include Solder)   |           | 1.15 |

| Maximum Component - 2   |           |      |

| side (include Solder)   |           | 0.2  |

| Total Maximum PCB       |           |      |

| Thickness               |           | 2.15 |

### 4.4. Exposed Areas and Restrictions

The display module shall not have exposed edges or components, which may cause injury or damage during handling, inspection, assembly, and service. Exposed areas of the display module (those not protected or shielded by construction) must be insulated and otherwise protected to eliminate the possibility of electrical shorting or destructive ESD discharges (per Section 7.2) during handling, inspection, assembly, and service. The Supplier shall identify all such areas prior to the Design Review and work with Apple Engineering to ensure the above criteria have been addressed.

## 5. ELECTRICAL REQUIREMENTS

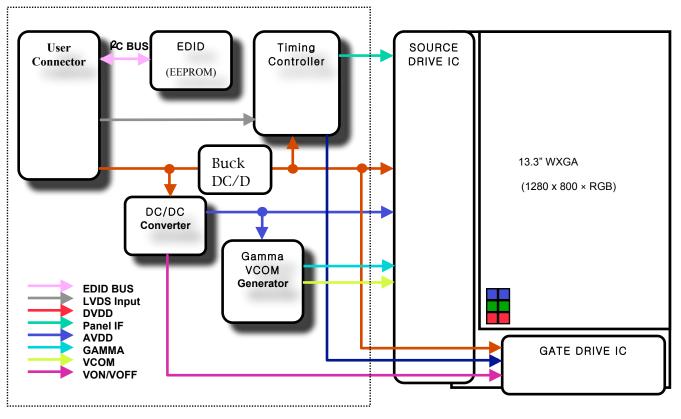

### 5.1. Block Diagram

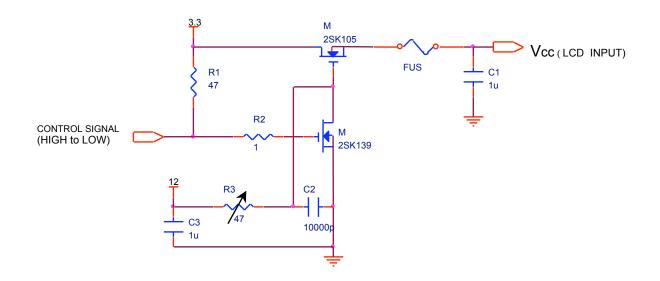

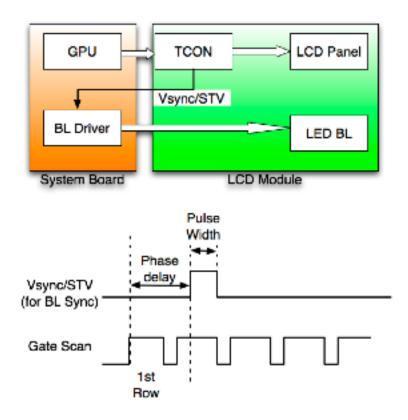

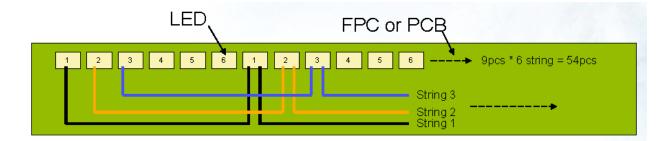

### Backlight Driving Architecture

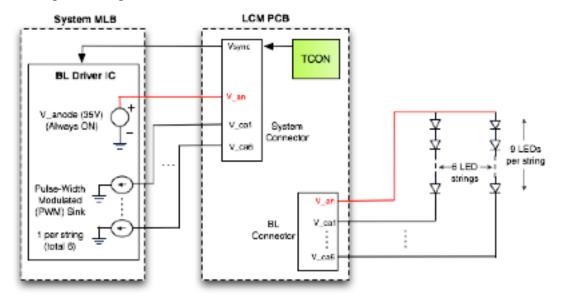

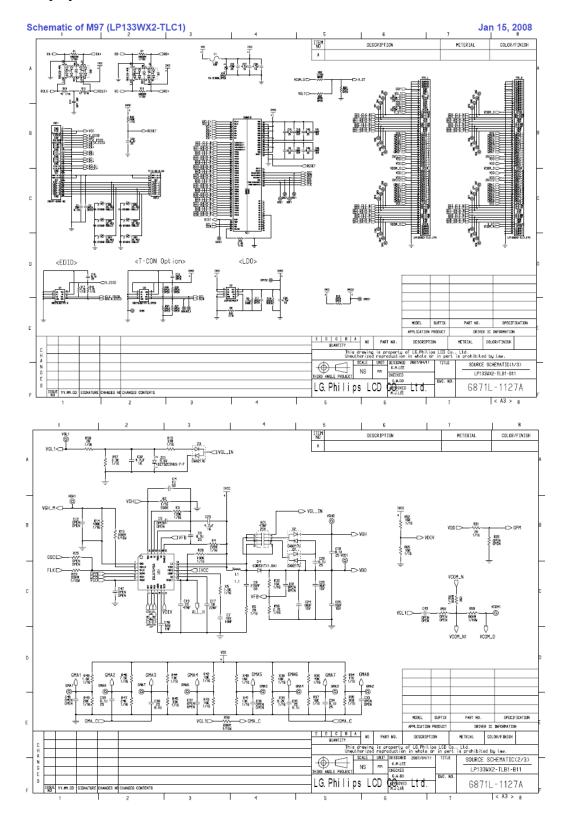

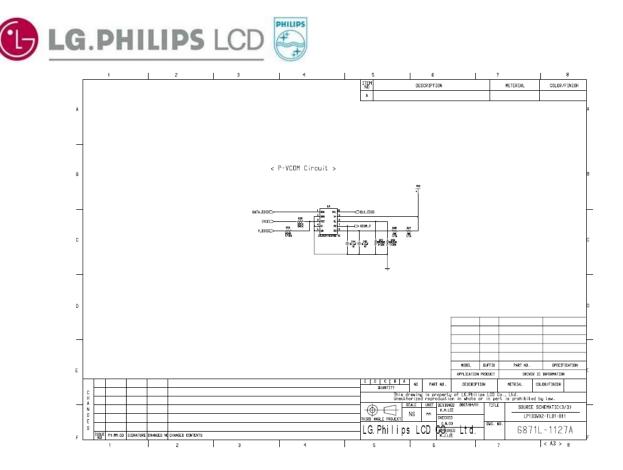

### 5.2. Display PCB Schematics

5.3. Display PCB Layout

Layer 1:

Layer 2:

Layer 3:

Layer 4:

Layer 5:

Layer 6:

100

Layer 7:

Layer 8:

5.4. Display Subsystem (PCB & TFT Panel)

5.4.1. Pin-Out (Single Channel LVDS Interface)

Connector: IPEX 20474-030E-12 or equivalent (1.0 mm thickness, lock-in type, pin 1 starts from left on the front)

Matching Connector: IPEX 20472-030T-10 or equivalent (micro-coax type)

Interface Chips: (need update according the latest Configuration Sheet), integrated LVDS and timing controller)

|     | Single Channel LVDS Configuration |                         |                                 |  |  |  |  |  |  |  |  |

|-----|-----------------------------------|-------------------------|---------------------------------|--|--|--|--|--|--|--|--|

| Pin | Symbol                            | Description             | Micro-coax cable gauge<br>(AWG) |  |  |  |  |  |  |  |  |

| 1   | GND                               | Ground                  | 40                              |  |  |  |  |  |  |  |  |

| 2   | Vcc                               | Power Supply (+3.3V)    | 36                              |  |  |  |  |  |  |  |  |

| 3   | V <sub>analog</sub>               | Power Supply (+3.3V)    | 36                              |  |  |  |  |  |  |  |  |

| 4   | V <sub>EDID</sub>                 | DDC Power +3.3V         | 40                              |  |  |  |  |  |  |  |  |

| 5   | Vsync                             | Vsync                   | 40                              |  |  |  |  |  |  |  |  |

| 6   | Clk <sub>EDID</sub>               | DDC Clock               | 40                              |  |  |  |  |  |  |  |  |

| 7   | DATA <sub>EDID</sub>              | DDC Data                | 40                              |  |  |  |  |  |  |  |  |

| 8   | Rin0-                             | Differential Data Input | 40                              |  |  |  |  |  |  |  |  |

| 9   | Rin0+                             | Differential Data Input | 40                              |  |  |  |  |  |  |  |  |

| <b>LG.P</b> | HILIPS LCD |                          |    |

|-------------|------------|--------------------------|----|

| 10          | GND        | Ground                   | 40 |

| 11          | Rin1-      | Differential Data Input  | 40 |

| 12          | Rin1+      | Differential Data Input  | 40 |

| 13          | GND        | Ground                   | 40 |

| 14          | Rin2-      | Differential Data Input  | 40 |

| 15          | Rin2+      | Differential Data Input  | 40 |

| 16          | GND        | Ground                   | 40 |

| 17          | Clkin-     | Differential Clock Input | 40 |

| 18          | Clkin+     | Differential Clock Input | 40 |

| 19          | GND        | Ground                   | 40 |

| 20          | NC         | NC                       | 40 |

| 21          | Vdc(1 &2)  | LED Annold (Positive)    | 40 |

| 22          | Vdc(3&4)   | LED Annold (Positive)    | 40 |

| 23          | NC         | NC                       | 40 |

| 24          | Vdc1       | LED Cathode (Negative)   | 40 |

| 25          | Vdc2       | LED Cathode (Negative)   | 40 |

| 26          | Vdc3       | LED Cathode (Negative)   | 40 |

| 27          | Vdc4       | LED Cathode (Negative)   | 40 |

| 28          | Vdc5       | LED Cathode (Negative)   | 40 |

| 29          | Vdc6       | LED Cathode (Negative)   | 40 |

| 30          | NC         | NC                       | 40 |

PHILIPS

### 5.4.3. Color Input Data Reference

The brightness of each primary color (red, green and blue) is based on the 6-bit gray scale data input for the color. The higher the binary input, the brighter the color. The table below provides a reference for color versus data input.

|        |                |     |    |    |    |    |    |    | Inp | ut Co | olor l | Data |    |         |    |    |    |    |    |

|--------|----------------|-----|----|----|----|----|----|----|-----|-------|--------|------|----|---------|----|----|----|----|----|

|        | Color          | Red |    |    |    |    |    |    | Gr  | een   |        |      |    |         | Bl | ue |    |    |    |

|        |                | Μ   | SB |    | LS | В  |    |    | MS  | В     |        | LSB  |    | MSB LSB |    |    |    |    |    |

|        |                | R5  | R4 | R3 | R2 | R1 | R0 | G5 | G4  | G3    | G2     | G1   | G0 | B5      | B4 | B3 | B2 | B1 | B0 |

|        | Black          | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0     | 0      | 0    | 0  | 0       | 0  | 0  | 0  | 0  | 0  |

|        | Red(63)        | 1   | 1  | 1  | 1  | 1  | 1  | 0  | 0   | 0     | 0      | 0    | 0  | 0       | 0  | 0  | 0  | 0  | 0  |

|        | Green(63)      | 0   | 0  | 0  | 0  | 0  | 0  | 1  | 1   | 1     | 1      | 1    | 1  | 0       | 0  | 0  | 0  | 0  | 0  |

| Basic  | Blue(63)       | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0     | 0      | 0    | 0  | 1       | 1  | 1  | 1  | 1  | 1  |

| Colors | Cyan           | 0   | 0  | 0  | 0  | 0  | 0  | 1  | 1   | 1     | 1      | 1    | 1  | 1       | 1  | 1  | 1  | 1  | 1  |

|        | Magenta        | 1   | 1  | 1  | 1  | 1  | 1  | 0  | 0   | 0     | 0      | 0    | 0  | 1       | 1  | 1  | 1  | 1  | 1  |

|        | Yellow         | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1   | 1     | 1      | 1    | 1  | 0       | 0  | 0  | 0  | 0  | 0  |

|        | White          | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1   | 1     | 1      | 1    | 1  | 1       | 1  | 1  | 1  | 1  | 1  |

|        | Red(00) Dark   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0     | 0      | 0    | 0  | 0       | 0  | 0  | 0  | 0  | 0  |

|        | Red(01)        | 0   | 0  | 0  | 0  | 0  | 1  | 0  | 0   | 0     | 0      | 0    | 0  | 0       | 0  | 0  | 0  | 0  | 0  |

|        | Red(02)        | 0   | 0  | 0  | 0  | 1  | 0  | 0  | 0   | 0     | 0      | 0    | 0  | 0       | 0  | 0  | 0  | 0  | 0  |

| Red    |                | :   | :  | :  | :  | :  | :  | :  | :   | :     | :      | :    | :  | :       | :  | :  | :  | :  | :  |

|        | Red(61)        | 1   | 1  | 1  | 1  | 0  | 1  | 0  | 0   | 0     | 0      | 0    | 0  | 0       | 0  | 0  | 0  | 0  | 0  |

|        | Red(62)        | 1   | 1  | 1  | 1  | 1  | 0  | 0  | 0   | 0     | 0      | 0    | 0  | 0       | 0  | 0  | 0  | 0  | 0  |

|        | Red(63) Bright | 1   | 1  | 1  | 1  | 1  | 1  | 0  | 0   | 0     | 0      | 0    | 0  | 0       | 0  | 0  | 0  | 0  | 0  |

|        | Green(00)Dark  | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0     | 0      | 0    | 0  | 0       | 0  | 0  | 0  | 0  | 0  |

|        | Green(01)      | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0     | 0      | 0    | 1  | 0       | 0  | 0  | 0  | 0  | 0  |

|        | Green(02)      | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0     | 0      | 1    | 0  | 0       | 0  | 0  | 0  | 0  | 0  |

| Green  |                | :   | :  | :  | :  | :  | :  | :  | :   | :     | :      | :    | :  | :       | :  | :  | :  | :  | :  |

|        | Green(61)      | 0   | 0  | 0  | 0  | 0  | 0  | 1  | 1   | 1     | 1      | 0    | 1  | 0       | 0  | 0  | 0  | 0  | 0  |

|        | Green(62)      | 0   | 0  | 0  | 0  | 0  | 0  | 1  | 1   | 1     | 1      | 1    | 0  | 0       | 0  | 0  | 0  | 0  | 0  |

### COLOR DATA REFERENCE

|      | Green(63)Bright | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

|------|-----------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|      | Blue(00) Dark   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|      | Blue(01)        | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

|      | Blue(02)        | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| Blue |                 | : | : | : | : | : | : | : | : | : | : | : | : | : | : | : | : | : | : |

|      | Blue(61)        | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 |

|      | Blue(62)        | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 |

|      | Blue(63) Bright | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

Pixel Format on the Display

Ver0.3

### 5.4.4. EDID Interface (Per Vesa EDID 1.x standard requirements)

# LP133WX2-TLC1 EDID Data

2008.07.12

| Byte#     | Byte# | Field Name and Commonto                                            | Va  | lue | Va   | lue  |                |

|-----------|-------|--------------------------------------------------------------------|-----|-----|------|------|----------------|

| (decimal) | (HEX) | Field Name and Comments                                            | (HI | EX) | (bin | ary) |                |

| 0         | 00    | Header                                                             | 0   | 0   | 0000 | 0000 |                |

| 1         | 01    | Header                                                             | F   | F   | 1111 | 1111 |                |

| 2         | 02    | Header                                                             | F   | F   | 1111 | 1111 |                |

| 3         | 03    | Header                                                             | F   | F   | 1111 | 1111 | Header         |

| 4         | 04    | Header                                                             | F   | F   | 1111 | 1111 |                |

| 5         | 05    | Header                                                             | F   | F   | 1111 | 1111 |                |

| 6         | 06    | Header                                                             | F   | F   | 1111 | 1111 |                |

| 7         | 07    | Header                                                             | 0   | 0   | 0000 | 0000 |                |

| 8         | 08    | EISA manufacturer code(3 Character<br>ID) = APP                    | 0   | 6   | 0000 | 0110 |                |

| 9         | 09    | Compressed ASCII                                                   | 1   | 0   | 0001 | 0000 |                |

| 10        | 0A    | Product code(Refer to Apple's request)<br>= M97(0x9c89)            | 8   | 9   | 1000 | 1001 |                |

| 11        | 0B    | (Hex, LSB first)                                                   | 9   | С   | 1001 | 1100 |                |

| 12        | 0C    | LCD module Serial No - Preferred but<br>Optional ("0" if not used) | 0   | 0   | 0000 | 0000 | Vender/        |

| 13        | 0D    | LCD module Serial No - Preferred but<br>Optional ("0" if not used) | 0   | 0   | 0000 | 0000 | Product ID     |

| 14        | 0E    | LCD module Serial No - Preferred but<br>Optional ("0" if not used) | 0   | 0   | 0000 | 0000 |                |

| 15        | 0F    | LCD module Serial No - Preferred but<br>Optional ("0" if not used) | 0   | 0   | 0000 | 0000 |                |

| 16        | 10    | Week of Manufacture = Jan 15th 3week                               | 0   | 3   | 0000 | 0011 |                |

| 17        | 11    | Year of Manufacture = 2008                                         | 1   | 2   | 0001 | 0010 |                |

| 18        | 12    | EDID Structure version # = 1                                       | 0   | 1   | 0000 | 0001 | EDID Version/  |

| 19        | 13    | EDID Revision # = 3                                                | 0   | 3   | 0000 | 0011 | Revision       |

| 20        | 14    | Video Input Definition = Digital I/P,non<br>TMDS CRGB              | 8   | 0   | 1000 | 0000 |                |

| 21        | 15    | Max H image size(cm)=28.608cm(29)                                  | 1   | D   | 0001 | 1101 | Display        |

| 22        | 16    | Max V image size(cm)=17.880cm(18)                                  | 1   | 2   | 0001 | 0010 | Parameter      |

| 23        | 17    | Display gamma =2.2                                                 | 7   | 8   | 0111 | 1000 |                |

| 24        | 18    | Feature support(DPMS) = Active off,<br>RGB Color                   | 0   | А   | 0000 | 1010 |                |

| 25        | 19    | Red/Green low Bits                                                 | D   | Α   | 1101 | 1010 |                |

| 26        | 1A    | Blue/White Low Bits                                                | Е   | 0   | 1110 | 0000 |                |

| 27        | 1B    | Red X = 0.597                                                      | 9   | 8   | 1001 | 1000 |                |

| 28        | 1C    | Red Y = 0.349                                                      | 5   | 9   | 0101 | 1001 |                |

| 29        | 1D    | Green X = 0.319                                                    | 5   | 1   | 0101 | 0001 | Color          |

| 30        | 1E    | Green Y = 0.549                                                    | 8   | С   | 1000 | 1100 | Characteristic |

**LG.PHILIPS** LCD

| 31 | 1F | Blue X = 0.144                                | 2 | 4 | 0010 | 0100 |             |

|----|----|-----------------------------------------------|---|---|------|------|-------------|

| 32 | 20 | Blue Y = 0.135                                | 2 | 2 | 0010 | 0010 |             |

| 33 | 21 | White X = 0.313                               | 5 | 0 | 0101 | 0000 |             |

| 34 | 22 | White Y = 0.329                               | 5 | 4 | 0101 | 0100 |             |

| 35 | 23 | Established Timing I = 00h(If not used)       | 0 | 0 | 0000 | 0000 | Established |

| 36 | 24 | Established Timing II = 00h(If not used)      | 0 | 0 | 0000 | 0000 | Timings     |

| 37 | 25 | Manufacturer's Timings = 00h(If not used)     | 0 | 0 | 0000 | 0000 |             |

| 38 | 26 | Standard Timing Identification 1 was not used | 0 | 1 | 0000 | 0001 |             |

| 39 | 27 | Standard Timing Identification 1 was not used | 0 | 1 | 0000 | 0001 |             |

| 40 | 28 | Standard Timing Identification 2 was not used | 0 | 1 | 0000 | 0001 |             |

| 41 | 29 | Standard Timing Identification 2 was not used | 0 | 1 | 0000 | 0001 |             |

| 42 | 2A | Standard Timing Identification 3 was not used | 0 | 1 | 0000 | 0001 |             |

| 43 | 2B | Standard Timing Identification 3 was not used | 0 | 1 | 0000 | 0001 |             |

| 44 | 2C | Standard Timing Identification 4 was not used | 0 | 1 | 0000 | 0001 | Standard    |

| 45 | 2D | Standard Timing Identification 4 was not used | 0 | 1 | 0000 | 0001 | Timing ID   |

| 46 | 2E | Standard Timing Identification 5 was not used | 0 | 1 | 0000 | 0001 |             |

| 47 | 2F | Standard Timing Identification 5 was not used | 0 | 1 | 0000 | 0001 |             |

| 48 | 30 | Standard Timing Identification 6 was not used | 0 | 1 | 0000 | 0001 |             |

| 49 | 31 | Standard Timing Identification 6 was not used | 0 | 1 | 0000 | 0001 |             |

| 50 | 32 | Standard Timing Identification 7 was not used | 0 | 1 | 0000 | 0001 |             |

| 51 | 33 | Standard Timing Identification 7 was not used | 0 | 1 | 0000 | 0001 |             |

| 52 | 34 | Standard Timing Identification 8 was not used | 0 | 1 | 0000 | 0001 |             |

| 53 | 35 | Standard Timing Identification 8 was not used | 0 | 1 | 0000 | 0001 |             |

| Byte#     | Byte# | Field Name and Comments                                  |     | lue | Va   | lue  |

|-----------|-------|----------------------------------------------------------|-----|-----|------|------|

| (decimal) | (HEX) | Field Marile and Comments                                | (HE | EX) | (bin | ary) |

| 54        | 36    | Pixel Clock/10,000 (LSB)<br>72.5 MHz @ 60.2Hz            | 5   | 2   | 0101 | 0010 |

| 55        | 37    | Pixel Clock/10,000 (MSB)                                 | 1   | С   | 0001 | 1100 |

| 56        | 38    | Horizontal Active (lower 8 bits)<br>1280 Pixels          | 0   | 0   | 0000 | 0000 |

| 57        | 39    | Horizontal Blanking(Thp-HA) (lower 8<br>bits) 143 Pixels | 8   | F   | 1000 | 1111 |

| 58         3A         Horizontal Active / Horizontal<br>Blanking(Thp-HA) (upper 4:4bits)         5         0         0101         0000           59         3B         Vertical Avtive<br>800 Lines         2         0         0010         0000           60         3C         Blanking (Trp-HA) (DE<br>Blanking (Trp-HA) (DE<br>Lines         2         0         0011         0000           61         3D         HA) (upper 4:4bits)         3         0         0011         0000           62         3E         Horizontal Sync. Offset (Thfp)         3         0         0011         0000           63         3F         Horizontal Sync. Offset(Tvp)         3         0         0011         0000           64         40         (VSPW)         3 Lines : 6         3         6         0011         1010           65         41         Horizontal Marge Size =         1         E         0001         1000           66         42         Horizontal Border = 0         0         0         0000         0000           67         43         Vertical Image Size =         1         E         0001         1100           68         44         Horizontal Sync. Offset/Width         0         0                                                                              |    |             |                                                                       |   |   |      |      |            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------------|-----------------------------------------------------------------------|---|---|------|------|------------|

| 59         38         Vertical Blanking (Tvp-HA) (DE<br>Blanking typ, for DE only panels)         46         2         E         0010         0000           60         3C         Vertical Blanking (Tvp-HA) (DE<br>Blanking typ, for DE only panels)         46         2         E         0010         1110           61         3D         HA/ (upper 4/4bits)         3         0         0011         0000           62         3E         Horizontal Sync. Offset (Thfp)         3         0         0011         0000           63         3F         Horizontal Sync. Offset (Tvfp) : Sync Width<br>(VSPW)         3 Lines : 6         3         6         0011         0110           64         40         Lines         1         E         0001         1110         #1           65         41         Horizontal Vertical Sync Offset/Width<br>(upper 2bits)         0         0         0000         0000         0000           66         42         Horizontal Border = 0         0         0         0         0000         0000           70         46         Vertical Border = 0         0         0         00000         0000           71         47         spaceriptor #2         0         0         00000         0000<                                                 | 58 | 3 3A        |                                                                       | 5 | 0 | 0101 | 0000 |            |

| 60         3C         Blanking typ.for DE only panels)         46         2         E         0010         1110           61         3D         Vertical Active : Vertical Blanking (Tvp-<br>HA) (upper 4.4bits)         3         0         0011         0000           62         3E         Horizontal Sync. Offset (Thfp)<br>48 Pixels         3         0         0011         0000         0000           63         3F         32 Pixels         2         0         0010         0000         0000         #1           64         40         (VSPW)         3 Lines : 6         3         6         0011         1010         #1           65         41         Horizontal Vertical Sync Offset/Width<br>(upper 2bits)         0         0         0000         0000         0000         0000         0000           66         42         286.08mm(286)         1         E         0001         1110         111         8         8         0         1         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         000                                                                | 59 | ) 3B        | Vertical Avtive                                                       | 2 | 0 | 0010 | 0000 |            |

| 61         3D         HA) (upper 4:4bits)         3         0         0011         0000         Participantal Sync. Offset (Thfp)         3         0         0011         0000         #a           62         3E         48 Pixels         3         0         0011         0000         0000         #d         #d         Pixels         Descriptor         #d         Ad         D         Do         Do         Do         Do         Do         Do         Do         Do         Do                                                      | 60 | ) 3C        | Vertical Blanking (Tvp-HA) (DE<br>Blanking typ.for DE only panels) 46 | 2 | E | 0010 | 1110 |            |

| 62         3e         48 Pixels         3e         0         0011         0000         Descriptor           63         3F         3E Pixels         Horizontal Sync Offset(Tvfp) : Sync Width<br>(VSPW)         2         0         0011         0110         0000         #1           64         40         Vertical Sync Offset(Tvfp) : Sync Width<br>(USPW)         3 Lines : 6         3         6         0011         0110         0100           65         41         Horizontal Vertical Sync Offset/Width<br>(upper 2bits)         0         0         0000         0000         0000           66         42         Horizontal Roge Size =         1         E         0001         1010           67         43         Vertical Border = 0         0         0         0000         0000           68         44         Horizontal Border = 0         0         0         0000         0000           70         46         Vertical Border = 0         0         0         0000         0000           71         47         Non-interlaceAl Normal display.no stereo.Digital<br>separate sync.HV pol regatives         0         0         0000         0000           75         48         Vertical link component format(6-bit<br>panel interface)                                 | 61 | I 3D        | HA) (upper 4:4bits)                                                   | 3 | 0 | 0011 | 0000 | Timing     |

| 6.3         3F         32 Pixels         2         0         0010         0000         With           64         40         Vertical Sync Offset(Tvfp) : Sync Width<br>Lines         3         6         0011         0110           65         41         Horizontal Vertical Sync Offset/Width<br>(upper 2bits)         0         0         0000         0000           66         42         Horizontal Image Size =<br>286.08mm(286)         1         E         0001         1110           68         44         Horizontal Border = 0         0         0         0000         0000           69         45         Horizontal Border = 0         0         0         0000         0000           70         46         Vertical Image Size         1         8         0001         1000           71         47         separate synch Vpol negatives         1         8         0001         0000           71         47         separate synch Vpol negatives         1         8         0001         1000           72         48         Detailed Timing Descriptor #2         0         0         00000         0000           76         4C         Version         0         0         00000                                                                                         | 62 | 2 3E        | 48 Pixels                                                             | 3 | 0 | 0011 | 0000 | Descriptor |

| 64         40         (VSPW)         3 Lines : 6         3         6         0011         0110           65         41         Horizontal Vertical Sync Offset/Width<br>(upper 2bits)         0         0         0000         0000           66         42         286.08mm(286)         1         E         0001         1110           67         43         Vertical Image Size =         1         0         0000         0000           68         44         Horizontal & Vertical Image Size =         1         0         0000         0000           69         45         Horizontal & Vertical Border = 0         0         0         00000         0000           70         46         Vertical Border = 0         0         0         00000         0000           71         47         Non-interfaced.Normal display.no stereo.Digital         1         8         0001         1000           72         48         Detailed Timing Descriptor #2         0         0         00000         0000           74         4A         0         0         0000         0000         0000           76         4C         Version         0         0         00000         0000                                                                                                            | 63 | 3 3F        | 32 Pixels                                                             | 2 | 0 | 0010 | 0000 | #1         |

| 65         41         (upper 2bits)         0         0         0         0         0         0         0000         0000         0000           66         42         Horizontal Image Size =<br>286.08mrQ286)         1         E         0001         1110           67         43         Vertical Image Size = 178.80cm(179)         B         3         1011         0011           68         44         Horizontal & Vertical Image Size         1         0         0000         0000           69         45         Horizontal & Vertical Border = 0         0         0         00000         0000           70         46         Vertical Border = 0         0         0         00000         0000           71         47         separate sync.HV pol negatives         1         8         0001         1000           72         48         Detailed Timing Descriptor #2         0         0         00000         0000           75         4B         0         1         00000         0000         0000           76         4C         Version         0         0         0000         0000           76         4D         Apple edid signature         1                                                                                                                    | 64 | 40          | (VSPW) 3 Lines : 6                                                    | 3 | 6 | 0011 | 0110 |            |

| 66         42         286.08mm(286)         1         E         0001         1110           67         43         Vertical Image Size = 178.80cm(179)         B         3         1011         0011           68         44         Horizontal & Vertical Image Size         1         0         0000         0000           69         45         Horizontal Border = 0         0         0         0000         0000           70         46         Vertical Border = 0         0         0         0000         0000           71         47         Separate SynchWy Dengatives         1         8         0001         1000           72         48         Detailed Timing Descriptor #2         0         0         00000         0000           75         48         0         1         0000         0000         0000           76         4C         Version         0         0         0000         0000           78         4F         Apple edid signature         1         0         0         00000         0000           80         50         Pixel and link component format(6-bit panel interface)         0         0         00000         0000                                                                                                                            | 65 | 5 41        |                                                                       | 0 | 0 | 0000 | 0000 |            |

| 68         44         Horizontal & Vertical Image Size         1         0         0001         0000           69         45         Horizontal Border = 0         0         0         0         0000         0000           70         46         Vertical Border = 0         0         0         0         0000         0000           71         47         Non-interaced, Normal display, no stereo, Digital separate sync, HVV pol negatives         1         8         0001         1000           72         48         Detailed Timing Descriptor #2         0         0         0000         0000           73         49         0         0         0000         0000         0000           74         4A         0         0         0000         0000         0000           75         4B         0         1         0000         0000         0000           76         4C         Version         0         0         0001         0000         0000           78         4E         Apple edid signature         1         0         0010         0000         0000           80         50         Pixel and link component format(6-bit panel interface)         0 <t< td=""><td>66</td><td>6 42</td><td></td><td>1</td><td>Е</td><td>0001</td><td>1110</td><td></td></t<>        | 66 | 6 42        |                                                                       | 1 | Е | 0001 | 1110 |            |

| 68         44         Horizontal & Vertical Image Size         1         0         0001         0000           69         45         Horizontal Border = 0         0         0         0         0000         0000           70         46         Vertical Border = 0         0         0         0         0000         0000           71         47         Non-interaced, Normal display, no stereo, Digital separate sync, HVV pol negatives         1         8         0001         1000           72         48         Detailed Timing Descriptor #2         0         0         0000         0000           73         49         0         0         0000         0000         0000           74         4A         0         0         0000         0000         0000           75         4B         0         1         0000         0000         0000           76         4C         Version         0         0         0001         0000         0000           78         4E         Apple edid signature         1         0         0010         0000         0000           80         50         Pixel and link component format(6-bit panel interface)         0 <t< td=""><td>67</td><td><b>′</b> 43</td><td></td><td>В</td><td>3</td><td>1011</td><td>0011</td><td></td></t<> | 67 | <b>′</b> 43 |                                                                       | В | 3 | 1011 | 0011 |            |

| 69         45         Horizontal Border = 0         0         0         0         0000         0000           70         46         Vertical Border = 0         0         0         0         0000         0000           71         47         Non-interfaced.Normal display.no stereo.Digital<br>separate sync,H/V pol negatives         1         8         0001         1000           72         48         Detailed Timing Descriptor #2         0         0         0000         0000           73         49         0         0         0000         0000         0000           74         4A         0         0         0         0000         0000           76         4E         Apple edid signature         0         6         0000         0000           77         4D         Apple edid signature         1         0         0000         0000           79         4F         Link Type         2         0         0100         0000         0000           80         50         Pixel and link component format(6-bit<br>panel interface)         0         0         00000         0000           83         53         0         0         0000000000         #2                                                                                                           | 68 | 3 44        |                                                                       | 1 | 0 | 0001 | 0000 |            |

| 70         46         Vertical Border = 0         0         0         0         0000         0000           71         47         Non-interfaced,Normal display, no stereo,Digital<br>separate sync,HV pol negatives         1         8         0001         1000           72         48         Detailed Timing Descriptor #2         0         0         0000         0000           73         49         0         0         0         0000         0000           74         4A         0         0         0         00000         0000           75         4B         0         1         0000         0000         0000           76         4C         Version         0         0         0000         0000           77         4D         Apple edid signature         1         0         0001         0000           79         4F         Link Type         2         0         0010         0000           80         50         Pixel and link component format(6-bit panel interface)         0         0         00000         000           81         51         Panel features(Inverter NA, no inverter)         0         0         000000         #2                                                                                                                         | 69 | 9 45        | °                                                                     |   | 0 |      |      |            |

| 71         47         Non-interlaced, Normal display, no stereo, Digital separate sync, HV pol negatives         1         8         0001         1000           72         48         Detailed Timing Descriptor #2         0         0         0000         0000         0000           73         49         0         0         0         0         0000         0000         0000           74         4A         0         0         0         0         0000         0000         0000           75         4B         0         1         0000         0000         0000         0000           76         4C         Version         0         6         0000         011         0000         0000           77         4D         Apple edid signature         1         0         0010         0000           79         4F         Link Type         2         0         0101         0000         0000         #2           80         50         Pixel and link component format(6-bit panel interface)         0         0         0000         0000         #2         #2         #2         #2         #2         #2         #2         #2         #2         #2                                                                                                                      |    |             |                                                                       |   | 0 |      |      |            |

| 73       49       0       0       0000       0000       0000         74       4A       0       0       0000       0000       0000         75       4B       0       1       0000       0000       0000         76       4C       Version       0       0       0000       0000       0000         77       4D       Apple edid signature       0       6       0000       0000       0000         78       4E       Apple edid signature       1       0       0011       0000       0000         79       4F       Link Type       2       0       0010       0000       0000         80       50       Pixel and link component format(6-bit panel interface)       0       0       0       0000       0000         81       51       Panel features(Inverter NA, no inverter)       0       0       00000       0000       #2         82       52       0       0       0       00000       0000       #2         84       54       0       0       0       00000       0000       #2         88       58       0       0       0       0 <t< td=""><td></td><td></td><td>Non-interlaced, Normal display, no stereo, Digital</td><td></td><td></td><td></td><td></td><td></td></t<>                                                                                                                  |    |             | Non-interlaced, Normal display, no stereo, Digital                    |   |   |      |      |            |

| 74       4A       0       0       0000       0000       0000         75       4B       0       1       0000       0001         76       4C       Version       0       0       0000       0000         77       4D       Apple edid signature       0       6       0000       0000       0000         77       4D       Apple edid signature       1       0       0001       0000       0000         79       4F       Link Type       2       0       0010       0000       0000         80       50       Pixel and link component format(6-bit panel interface)       0       0       0       00000       0000       0000       0000       0000       #2         81       51       Panel features(Inverter NA, no inverter)       0       0       00000       0000       #2       #2         82       52       0       0       0       00000       0000       0000       #2         84       54       0       0       0       00000       0000       86       56       0       0       00000       0000         88       58       0       0       0                                                                                                                                                                                                                                                | 72 | 2 48        | Detailed Timing Descriptor #2                                         | 0 | 0 | 0000 | 0000 |            |

| 75       4B       0       1       0000       0001         76       4C       Version       0       0       0000       0000         77       4D       Apple edid signature       0       6       0000       0110         78       4E       Apple edid signature       1       0       0001       0000         79       4F       Link Type       2       0       0010       0000       0000         80       50       Pixel and link component format(6-bit panel interface)       0       0       0       0000       0000       0000       #2         81       51       Panel features(Inverter NA, no inverter)       0       0       00000       0000       #2       #2         82       52       0       0       0       0000       0000       #2       #2         83       53       0       0       00000       0000       #2       #2       #2         86       56       0       0       00000       0000       0000       0000       4         88       58       0       0       0       0000       0000       0000         90       5A <td< td=""><td>73</td><td>3 49</td><td>• ·</td><td>0</td><td>0</td><td>0000</td><td>0000</td><td></td></td<>                                                                                                                                                | 73 | 3 49        | • ·                                                                   | 0 | 0 | 0000 | 0000 |            |

| 76         4C         Version         0         0         0         0000         0000           77         4D         Apple edid signature         0         6         0000         0110           78         4E         Apple edid signature         1         0         0001         0000           79         4F         Link Type         2         0         0010         0000           80         50         Pixel and link component format(6-bit panel interface)         0         0         0         0000         0000           81         51         Panel features(Inverter NA, no inverter)         0         0         00000         0000         #2           82         52         0         0         0         00000         0000         #2           83         53         0         0         0         00000         0000         #2           84         54         0         0         0         00000         0000         86         56         0         0         00000         0000           85         55         0         0         0         00000         0000         90         5A         Detailed Timing Descriptor #3 <td>74</td> <td>4A</td> <td></td> <td>0</td> <td>0</td> <td>0000</td> <td>0000</td> <td></td>                                          | 74 | 4A          |                                                                       | 0 | 0 | 0000 | 0000 |            |

| 76         4C         Version         0         0         0         0000         0000           77         4D         Apple edid signature         0         6         0000         0110           78         4E         Apple edid signature         1         0         0001         0000           79         4F         Link Type         2         0         0010         0000           80         50         Pixel and link component format(6-bit panel interface)         0         0         0         0000         0000           81         51         Panel features(Inverter NA, no inverter)         0         0         00000         0000         #2           82         52         0         0         0         00000         0000         #2           83         53         0         0         0         00000         0000         #2           84         54         0         0         0         00000         0000         86         56         0         0         00000         0000           85         55         0         0         0         00000         0000         90         5A         Detailed Timing Descriptor #3 <td>75</td> <td>5 4B</td> <td></td> <td>0</td> <td>1</td> <td>0000</td> <td>0001</td> <td></td>                                        | 75 | 5 4B        |                                                                       | 0 | 1 | 0000 | 0001 |            |

| 77         4D         Apple edid signature         0         6         0000         0110           78         4E         Apple edid signature         1         0         0001         0000           79         4F         Link Type         2         0         0010         0000           80         50         Pixel and link component format(6-bit panel interface)         0         0         0         0000         0000           81         51         Panel features(Inverter NA, no inverter)         0         0         0         0000         0000         #2           82         52         0         0         0         0         00000         0000         #2           84         54         0         0         0         00000         0000         #2           85         55         0         0         0         00000         0000         #2           86         56         0         0         0         00000         0000         0000           87         57         0         0         0         00000         0000         0000           90         5A         Detailed Timing Descriptor #3         0                                                                                                                                                        |    |             | Version                                                               | 0 | 0 |      |      |            |

| 78         4E         Apple edid signature         1         0         0001         0000           79         4F         Link Type         2         0         0010         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0                                                                     | 77 | 7 4D        | Apple edid signature                                                  | 0 | 6 | 0000 |      |            |

| 79         4F         Link Type         2         0         0010         0000         Timing           80         50         Pixel and link component format(6-bit panel interface)         0         0         0         0000         0000         0000         0000         0000         #2           81         51         Panel features(Inverter NA, no inverter)         0         0         0         0000         0000         #2         #2           82         52         0         0         0         0         0         0000         0000         #2           83         53         0         0         0         00000         0000         #2           84         54         0         0         0         0000         0000         #2           85         55         0         0         0         0000         0000         #2           86         56         0         0         0         0000         0000         0000           87         57         0         0         0         0000         0000         0000           90         5A         Detailed Timing Descriptor #3         0         0         00000 </td <td>-</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                   | -  |             |                                                                       |   |   |      |      |            |

| 80         50         Pixel and link component format(6-bit panel interface)         0         0         0000         0000         Description           81         51         Panel features(Inverter NA, no inverter)         0         0         0000         0000         0000         #2           82         52         0         0         0         0         0000         0000         #2           83         53         0         0         0         0         0         0000         0000         #2           84         54         0         0         0         0         0000         0000         #2           85         55         0         0         0         0         0000         0000         #2           86         56         0         0         0         0000         0000         0000           87         57         0         0         0         00000         0000           88         58         0         0         0         00000         0000           90         5A         Detailed Timing Descriptor #3         0         0         0         0         00000         0000         92     <                                                                                                                                                            |    |             |                                                                       |   |   |      |      | Timina     |

| 81         51         Panel features (Inverter NA, no inverter)         0         0         0000         0000         #2           82         52         0         0         0         0         0000         0000           83         53         0         0         0         0         0000         0000           84         54         0         0         0         0000         0000           85         55         0         0         0         00000         0000           86         56         0         0         0         00000         0000           87         57         0         0         0         00000         0000           88         58         0         0         0         00000         0000           90         5A         Detailed Timing Descriptor #3         0         0         00000         0000           91         5B         0         0         0         00000         0000         0000           92         5C         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                   |    |             | Pixel and link component format(6-bit                                 |   | - |      |      | -          |

| 82         52         0         0         0         0000         0000           83         53         0         0         0         0000         0000           84         54         0         0         0         0000         0000           85         55         0         0         0         0000         0000           86         56         0         0         0000         0000           87         57         0         0         0000         0000           88         58         0         A         0000         0000           90         5A         Detailed Timing Descriptor #3         0         0         00000         0000           91         5B         0         0         00000         0000         0000           92         5C         0         0         0         00000         0000           93         5D         F         E         1111         1110           94         5E         0         0         0         00000         0000                                                                                                                                                                                                                                                                                                                        | 81 | 51          |                                                                       | 0 | 0 | 0000 | 0000 | #2         |

| 83       53       0       0       0000       0000         84       54       0       0       0000       0000         85       55       0       0       0000       0000         86       56       0       0       0000       0000         87       57       0       0       0000       0000         88       58       0       A       0000       1010         89       59       2       0       0010       0000         90       5A       Detailed Timing Descriptor #3       0       0       00000       0000         91       5B       0       0       0       00000       0000       0000         93       5D       F       E       1111       1110         94       5E       0       0       0       00000       0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |             |                                                                       |   |   |      |      | =          |

| 84       54       0       0       0000       0000         85       55       0       0       0000       0000         86       56       0       0       0000       0000         87       57       0       0       0000       0000         88       58       0       A       0000       1010         89       59       2       0       0010       0000         90       5A       Detailed Timing Descriptor #3       0       0       0000       0000         91       5B       0       0       00000       0000       0000         93       5D       F       E       1111       1110         94       5E       0       0       0       0000       0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -  |             |                                                                       |   |   |      |      |            |

| 85       55       0       0       0000       0000         86       56       0       0       0000       0000         87       57       0       0       0000       0000         88       58       0       A       0000       1010         89       59       2       0       0010       0000         90       5A       Detailed Timing Descriptor #3       0       0       00000       0000         91       5B       0       0       00000       0000       0000         92       5C       0       0       00000       0000         93       5D       F       E       1111       1110         94       5E       0       0       0       0000       0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |             |                                                                       |   |   |      |      |            |

| 86         56         0         0         0000         0000           87         57         0         0         0000         0000           88         58         0         A         0000         1010           89         59         2         0         0010         0000           90         5A         Detailed Timing Descriptor #3         0         0         00000         0000           91         5B         0         0         00000         0000         0000           92         5C         0         0         00000         0000         0000           93         5D         F         E         1111         1110           94         5E         0         0         0         00000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |             |                                                                       |   |   |      |      |            |

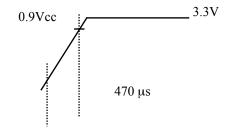

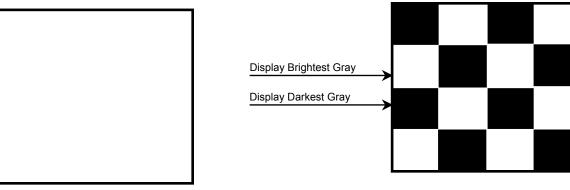

| 87       57       0       0       0000       0000         88       58       0       A       0000       1010         89       59       2       0       0010       0000         90       5A       Detailed Timing Descriptor #3       0       0       0000       0000         91       5B       0       0       0000       0000         92       5C       0       0       0000       0000         93       5D       F       E       1111       1110         94       5E       0       0       0       0000       0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |             |                                                                       |   |   |      |      |            |