# TFT COLOR LCD MODULE NL3224AC35-01

# 14 cm (5.5 Type), 320 × 240 Pixels, Full color NTSC/PAL mode, Incorporated backlight with inverter

NL3224AC35-01 is a TFT (thin film transistor) active matrix color liquid crystal display (LCD) comprising amorphous silicon TFT attached to each signal electrode, a driving circuit and a backlight. NL3224AC35-01 has a built-in backlight.

The 14 cm diagonal display area contains 320×240 pixels and can display full-color simultaneously.

#### 1. FEATURES

- o Analog RGB interface

- Low reflection

- o High luminance

- o NTSC/PAL mode

- o Reversible horizontal and vertical scanning

- o 234/240 line display

- o Incorporated edge type backlight

- o Designed viewing direction: 10 and 2 o'clock

#### 2. APPLICATIONS

- o Car navigations

- o TV monitors

- o Video games

- Monitors for process controller

#### 3. STRUCTURE AND FUNCTIONS

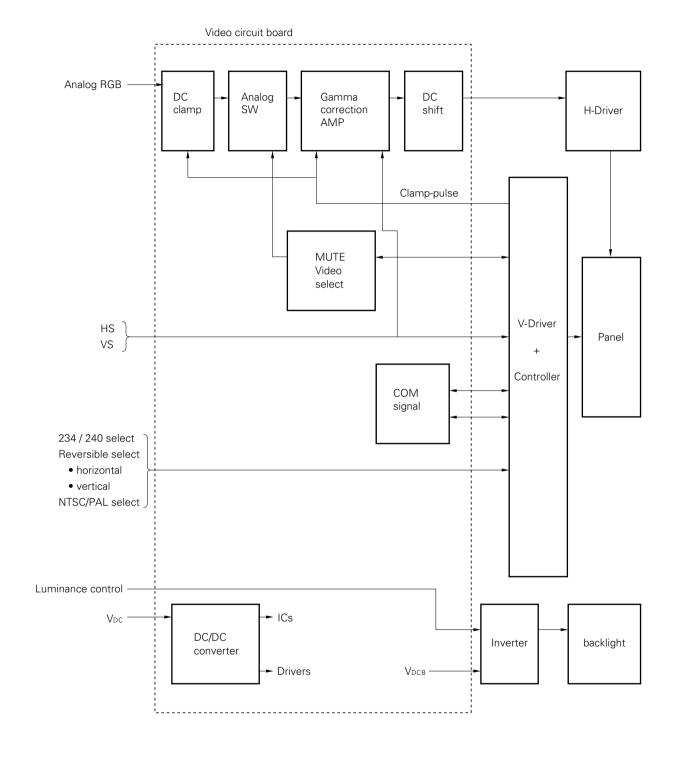

A TFT color LCD module comprises a TFT LCD panel, LSIs for driving liquid crystal, and a backlight. The TFT LCD panel is composed of a TFT array glass substrate superimposed on a color filter glass substrate with liquid crystal filled in the narrow gap between two substrates. The backlight apparatus is located on the backside of the LCD panel.

RGB (Red, Green, Blue) data signals are sent to LCD panel drivers after modulation into suitable forms for active matrix addressing through signal processor.

Each of the liquid crystal cells acts as an electro-optical switch that controls the light transmission from the backlight by a signal applied to a signal electrode through the TFT switch.

#### 4. OUTLINE OF CHARACTERISTICS (at room temperature)

Display area  $111.36 \text{ (H)} \times 83.52 \text{ (V)} \text{ mm}$  Drive system a-Si TFT active matrix

Display colors Full-color Number of pixels  $320 \times 240$

Pixel arrangement RGB vertical stripe Pixel pitch 0.348 (H)  $\times$  0.348 (V) mm

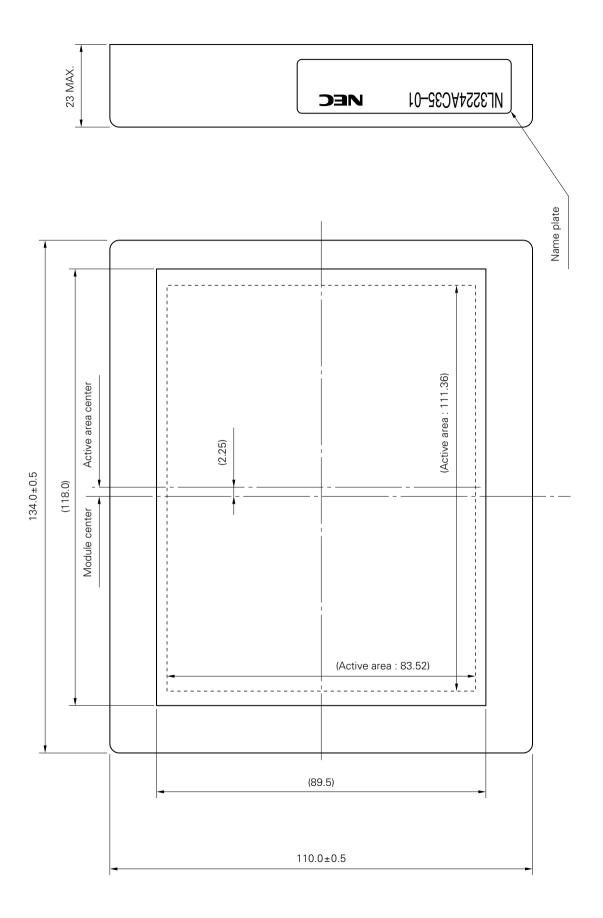

Module size  $134.0 \text{ (H)} \times 110.0 \text{ (V)} \times 23.0 \text{ max.(D)} \text{ mm}$

Weight 315 g (typ.) Contrast ratio 85:1 (typ.)

Viewing angle (more than the contrast ratio of 10:1)

• Horizontal: 45° (typ. left side, right side)

• Vertical: 30° (typ. up side), 15° (typ. down side)

Designed viewing direction

wider viewing angle with contrast ratio : 10 and 2 o'clock

wider viewing angle without image reversal : down side (6 o'clock)

• optimum grayscale ( $\gamma$  =2.2) : perpendicular

Color gamut 50% (typ. center, to NTSC)

Response time 50 ms (max.), "white" to "black"

Luminance 250 cd/m<sup>2</sup> (typ.)

Signal system

Analog RGB signals, synchronous signals (CLK, HS, VS)

Supply voltage

9.5 V (LCD power supply), 9.5 V (Backlight power supply)

Backlight

Edge light type, one fluorescent lamp (cold cathode type)

Power consumption 6.6 W (typ.)

# **5. BLOCK DIAGRAM**

#### 6. SPECIFICATION

# **6.1 GENERAL SPECIFICATIONS**

| Item              | Specifications                                          | Unit  |

|-------------------|---------------------------------------------------------|-------|

| Module size       | $134.0\pm0.5$ (H) × $110.0\pm0.5$ (V) × $23.0$ max. (D) | mm    |

| Display area      | 111.36 (H) × 83.52 (V)                                  | mm    |

| Number of dots    | 320 × 3 (H) × 240 (V)                                   | dot   |

| Dot pitch         | 0.116 (H) × 0.348 (V)                                   | mm    |

| Pixel pitch       | 0.348 (H) × 0.348 (V)                                   | mm    |

| Pixel arrangement | RGB (Red, Green, Blue) vertical stripe                  | -     |

| Display colors    | Full-color                                              | color |

| Weight            | 330 (max.)                                              | g     |

**note**: An inverter is incorporated with the module.

# **6.2 ABSOLUTE MAXIMUM RATINGS**

| Parameter               | Symbol | Ratings                                                                | Unit    | Remarks                             |  |  |

|-------------------------|--------|------------------------------------------------------------------------|---------|-------------------------------------|--|--|

| Committee               | VDC    | -0.5 to 20.0                                                           | V       | T- 25°C                             |  |  |

| Supply voltage          | VDCB   | -0.5 to 20.0                                                           | V       | Ta=25°C                             |  |  |

| Analog RGB input signal | Vin1   | -2.5 to 2.5                                                            | V       | Ta=25°C<br>- V <sub>DC</sub> =9.5 V |  |  |

| Logic input voltage     | VIN2   | -0.5 to 5.5                                                            | V       |                                     |  |  |

| Storage temp.           | Тѕт    | -40 to 95                                                              | °C      | _                                   |  |  |

| Operating temp.         | Тор    | –30 to 85                                                              | °C      | Module surface*                     |  |  |

|                         | •      | 95% relative humidity                                                  | Ta=40°C |                                     |  |  |

| Humidity                |        | 85% relative humidity                                                  | Ta=50°C | no                                  |  |  |

|                         |        | Absolute humidity shall not excee<br>Ta=50°C, 85% relative humidity le | Ta>50°C | condensation                        |  |  |

<sup>\*</sup> measured at the center of the display area

# **6.3 ELECTRICAL CHARACTERISTICS**

# (1) Power supply, logic input

Ta = 25°C

| Parameter                | Symbol           | min. | typ.  | max. | Unit | Remarks                                         |

|--------------------------|------------------|------|-------|------|------|-------------------------------------------------|

| Supply voltage           | V <sub>D</sub> C | 8.0  | 9.5   | 13.0 | V    | For processor,<br>controller and driver         |

|                          | VDCB             | 8.0  | 9.5   | 13.0 | V    | For backlight                                   |

| Logic input "L" voltage  | VIL              | 0    | _     | 0.9  | V    |                                                 |

| Logic input "H" voltage  | ViH              | 3.15 | _     | 5.0  | V    |                                                 |

| Logic output "L" voltage | Vol              | 0    | -     | 0.3  | ٧    | _                                               |

| Logic output "H" voltage | Vон              | 4.5  | _     | 5.0  | V    |                                                 |

| Supply ourrent           | IDC              | _    | (147) | 200  | mA   | At dot-checkered pattern ( $V_{DC} = 9.5 V$ )   |

| Supply current           | Ідсв             | -    | (541) | 600  | mA   | Maximum luminance<br>(V <sub>DCB</sub> = 9.5 V) |

# (2) Analog RGB signals

$Ta = 25^{\circ}C$

| Parameter                                | min. | typ. | max. | Unit | Remarks             |

|------------------------------------------|------|------|------|------|---------------------|

| Analog RGB input voltage (white - black) | 0    | _    | 0.7  | Vp-p | Zi = 75 Ω           |

| DC input level (black level)             | -1.0 | _    | 1.0  | V    | ZI = 75 \(\Omega\)2 |

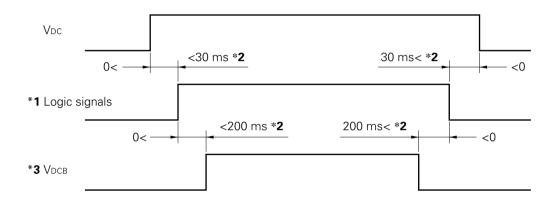

# **6.4 SUPPLY VOLTAGE SEQUENCE**

- \*  ${\bf 1}$  When the V  ${\tt DC}$  is off, please keep whole logic signals low level

- \* 2 Reference value

- \* 3 Apply V DCB within the LCD operation period. When the backlight turns on before LCD operation or the LCD operation turns off before the backlight turns off, the display may momentarily become white.

# **6.5 INTERFACE PIN CONNECTION**

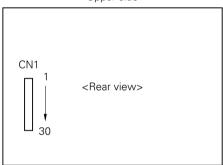

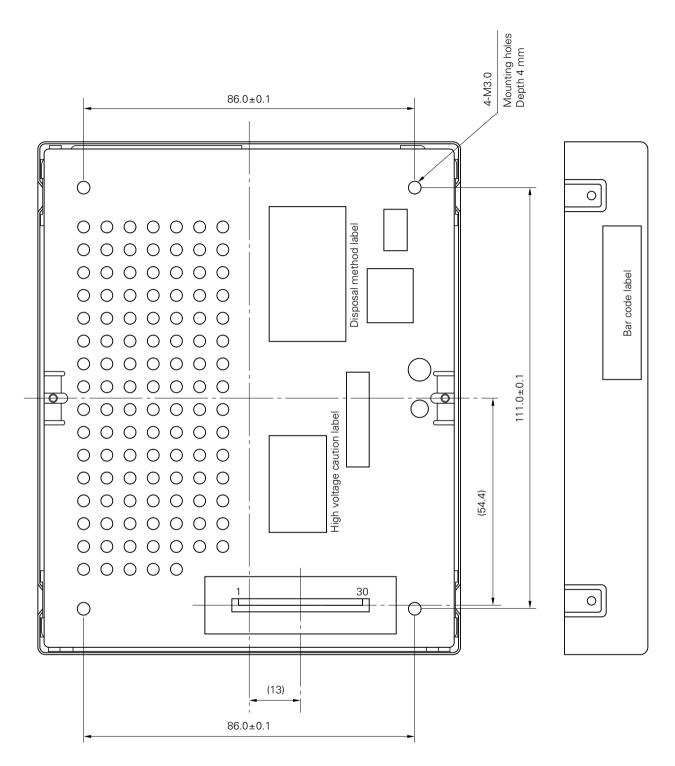

#### (1) Connector (CN1)

Part no. : 52610-3017 Supplier : Molex

Adaptable cable: SUMI-CARD 1.0 mm pitch 30 wick 85°C quality

Supplier: SUMITOMO ELECTRIC INDUSTRIES, LTD.

| Pin No. | Symbol           | Pin No. | Symbol           | Pin No. | Symbol |

|---------|------------------|---------|------------------|---------|--------|

| 1       | GNDD             | 11      | EXTCSL           | 21      | GNDD   |

| 2       | EXTCLK           | 12      | GNDD             | 22      | GNDD   |

| 3       | GNDD             | 13      | N/P              | 23      | GNDD   |

| 4       | HS               | 14      | MTSL             | 24      | GNDA   |

| 5       | VS               | 15      | U/D              | 25      | R      |

| 6       | HOUT             | 16      | R/L              | 26      | GNDA   |

| 7       | VOUT             | 17      | GNDD             | 27      | G      |

| 8       | B <sub>PLS</sub> | 18      | V <sub>DCB</sub> | 28      | GNDA   |

| 9       | GNDD             | 19      | V <sub>DCB</sub> | 29      | В      |

| 10      | GNDD             | 20      | VDC              | 30      | GNDA   |

#### <Connector location>

# Upper side

Lower side

# **6.6 PIN DESCRIPTION**

| Symbol           | In/Out | Logic    | Description                                                                                                                |  |  |  |  |

|------------------|--------|----------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| R                | ln     | -        | Analog Red signal 0.7 Vp-p Zi=75 $\Omega$                                                                                  |  |  |  |  |

| G                | ln     | -        | Analog Green signal 0.7 Vp-p Zi=75 Ω                                                                                       |  |  |  |  |

| В                | ln     | _        | Analog Blue signal 0.7 Vp-p Zi=75 Ω                                                                                        |  |  |  |  |

| EXTCLK           | In *1  | Negative | External clock EXTCLK becomes active, when EXTCSL is "H".                                                                  |  |  |  |  |

| HS               | In *1  | Negative | Horizontal synchronous signal                                                                                              |  |  |  |  |

| VS               | In *1  | Negative | Vertical synchronous signal                                                                                                |  |  |  |  |

| HOUT             | Out *1 | Negative | Horizontal synchronous signal output                                                                                       |  |  |  |  |

| VOUT             | Out *1 | Negative | Vertical synchronous signal output                                                                                         |  |  |  |  |

| EXTCSL           | In *1  | -        | Clock select signal H: external clock Default value is L L: internal clock                                                 |  |  |  |  |

| R/L              | ln *1  | -        | Horizontal scanning select signal  Default value is L  H: Right scanning  L: Left scanning                                 |  |  |  |  |

| U/D              | ln *1  | -        | Vertical scanning select signal  Default value is L  H: down scanning  L: up scanning                                      |  |  |  |  |

| N/P              | ln *1  | -        | Display mode select H : PAL mode Default value is L L : NTSC mode                                                          |  |  |  |  |

| MTSL             | In *1  | -        | Vertical display area select signal  Default value is L  H: 240 lines  L: 234 lines                                        |  |  |  |  |

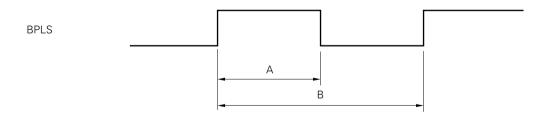

| BPLS             | In *1  | -        | Luminance control signal (pulse input) Luminance is controlled by the pulse width. Duty 100%: luminance max. Refer to P13. |  |  |  |  |

| VDC              | ln     | _        | Power supply for processor, controller and driver (+9.5 V)                                                                 |  |  |  |  |

| V <sub>DCB</sub> | ln     | _        | Power supply for backlight (+9.5 V)                                                                                        |  |  |  |  |

| GNDA             | _      | _        | Ground for analog RGB signal                                                                                               |  |  |  |  |

| GNDD             | _      | _        | Ground for logic and backlight                                                                                             |  |  |  |  |

<sup>\*1:</sup> CMOS level

# 6.7 SIGNALS

| No. | Functions                      | Description                                                                                                                                               |

|-----|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Reversible horizontal scanning | R/L signal is able to reverse scanning direction. (Right → Left or Left → Right)                                                                          |

| 2   | Reversible vertical scanning   | U/D signal is able to reverse scanning direction. (Up → Down or Down → Up)                                                                                |

| 3   | NTSC/PAL mode                  | N/P signal is able to change operating mode.  (NTSC → PAL or PAL → NTSC)  Scanning line is thinned out at the rate of seven to six lines in the PAL mode. |

| 4   | 234/240 line display           | MTSL signal is able to change scanning line. (234 lines → 240 lines or 240 lines → 234 lines)                                                             |

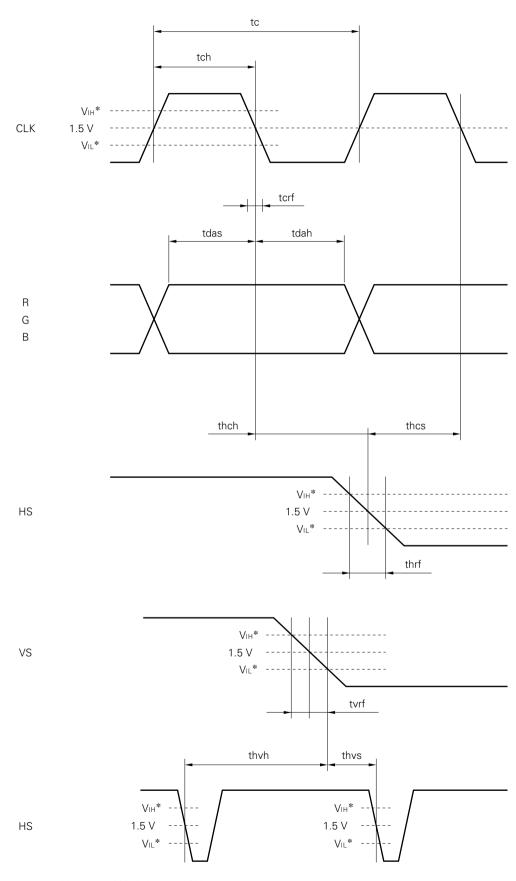

# **6.8 INPUT SIGNAL TIMING**

# (1) mode: NTSC, internal CLK

|     | Parameter                           | Symbol   | min.        | typ.           | max.          | Unit      | Remarks              |

|-----|-------------------------------------|----------|-------------|----------------|---------------|-----------|----------------------|

| CLK | Frequency                           | 1 / tc   | -           | 6.36<br>157.32 | _<br>_        | MHz<br>ns | -                    |

|     | Rise/fall                           | tcrf     | -           | -              | 70            | ns        | _                    |

|     | Duty                                | tch / tc | 0.4         | 0.5            | 0.6           | -         | -                    |

| HS  | Frequency                           | th       | 60.38<br>-  | 63.56<br>404   | 66.74<br>-    | μs<br>CLK | 15.734 kHz<br>(typ.) |

|     | Display                             | thd      | -<br>-      | 50.34<br>320   | -<br>-        | μs<br>CLK | -                    |

|     | Pulse-width                         | thp      | 1.0         | 4.7<br>30      | -<br>-        | μs<br>CLK | -                    |

|     | Pulse-width<br>+back-porch          | thpb     | -           | 11.01<br>70    | -<br>-        | μs<br>CLK | 234 line             |

|     |                                     | шрь      | _<br>_      | 12.11<br>77    | <u>-</u><br>- | μs<br>CLK | 240 line             |

|     | CLK-Hsync timing<br>hold/setup time | thch     | 10.0        | -              | _             | ns        | _                    |

|     |                                     | thcs     | 10.0        | -              | _             | ns        | _                    |

|     | V-Hsync timing                      | thvh     | 1           | -              | _             | CLK       | _                    |

|     | hold/setup time                     | thvs     | 10.0        | -              | -             | ns        | _                    |

|     | Rise/fall                           | thrf     | -           | -              | 10.0          | ns        | _                    |

| VS  | Frequency                           | tv       | 15.85<br>–  | 16.68<br>262.5 | 17.51<br>–    | ms<br>H   | 59.94 Hz<br>(typ.)   |

|     | Display                             |          | -<br>-      | 14.87<br>234   | -<br>-        | ms<br>H   | 234 line             |

|     |                                     | tvd      | -<br>-      | 15.25<br>240   | -<br>-<br>-   | ms<br>H   | 240 line             |

|     | Pulse-width                         | tvp      | 158.89<br>– | 190.67<br>3    | -<br>-        | μs<br>Η   | -                    |

|     | Pulse-width<br>+back-porch          | tvpb     | -<br>-      | 1.33<br>21     | -<br>-        | ms<br>H   | -                    |

|     | Rise/fall                           | tvrf     | _           | _              | 10.0          | ns        | _                    |

note 1: In the display start period (pulse-width + back-porch), analog RGB signals should be blanking level.

# (2) mode: PAL, internal CLK

|     | Parameter                           | Symbol   | min.        | typ.           | max.        | Unit      | Remarks              |

|-----|-------------------------------------|----------|-------------|----------------|-------------|-----------|----------------------|

| CLK | Frequency                           | 1 / tc   | _<br>_      | 6.45<br>154.96 | _<br>_      | MHz<br>ns | -                    |

|     | Rise/fall                           | tcrf     | -           | _              | 70          | ns        | _                    |

|     | Duty                                | tch / tc | 0.4         | 0.5            | 0.6         | -         | _                    |

| HS  | Frequency                           | th       | 60.80<br>–  | 64.00<br>413   | 67.20<br>–  | μs<br>CLK | 15.625 kHz<br>(typ.) |

|     | Display                             | thd      | -<br>-      | 49.60<br>320   | -<br>-      | μs<br>CLK | -                    |

|     | Pulse-width                         | thp      | 1.0         | 4.7<br>30      | -<br>-      | μs<br>CLK | -                    |

|     | Pulse-width<br>+back-porch          | thpb     | -           | 11.93<br>77    | -           | μs<br>CLK | 234 line             |

|     |                                     |          | _<br>_      | 12.71<br>82    | _<br>_      | μs<br>CLK | 240 line             |

|     | CLK-Hsync timing<br>hold/setup time | thch     | 10.0        | _              | _           | ns        | _                    |

|     |                                     | thcs     | 10.0        | _              | -           | ns        | _                    |

|     | V-Hsync timing<br>hold/setup time   | thvh     | 1           | -              | -           | CLK       | _                    |

|     |                                     | thvs     | 10.0        | -              | -           | ns        | _                    |

|     | Rise/fall                           | thrf     | -           | _              | 10.0        | ns        | _                    |

| VS  | Frequency                           | tv       | 19.00<br>–  | 20.00<br>312.5 | 21.00<br>–  | ms<br>H   | 50.00 Hz<br>(typ.)   |

|     | Display                             |          | -<br>-      | 17.47<br>273   | -<br>-      | ms<br>H   | 234 line             |

|     |                                     | tvd      | -<br>-<br>- | 17.92<br>280   | -<br>-      | ms<br>H   | 240 line             |

|     | Pulse-width                         | tvp      | 153.60<br>– | 192.00<br>2.5  |             | μs<br>Η   | -                    |

|     | Pulse-width<br>+back-porch          | to colo  | -<br>-      | 1.86<br>29     | -<br>-      | ms<br>H   | 234 line             |

|     |                                     | tvpb     | -<br>-<br>- | 1.66<br>26     | -<br>-<br>- | ms<br>H   | 240 line             |

|     | Rise/fall                           | tvrf     | _           | _              | 10.0        | ns        | _                    |

**note 1**: In the display start period (pulse-width + back-porch), analog RGB signals should be blanking level.

# (3) mode : NTSC, external CLK

|         | Parameter                           | Symbol   | min.          | typ.           | max.              | Unit      | Remarks              |

|---------|-------------------------------------|----------|---------------|----------------|-------------------|-----------|----------------------|

| EXTCLK  | Frequency                           | 1 / tc   | -<br>118.75   | 8.0<br>125.00  | -<br>131.25       | MHz<br>ns | -                    |

|         | Rise/fall                           | terf     | -             | -              | 10                | ns        | _                    |

|         | Duty                                | tch / tc | 0.4           | 0.5            | 0.6               | _         | _                    |

| HS      | Frequency                           | th       | 60.38<br>-    | 63.56<br>508   | 66.74<br>-        | μs<br>CLK | 15.734 kHz<br>(typ.) |

|         | Display                             | thd      | -             | 40.00<br>320   |                   | μs<br>CLK | -                    |

|         | Pulse-width                         | thp      | 1.0<br>-      | 4.7<br>38      |                   | μs<br>CLK | -                    |

|         | Pulse-width<br>+back-porch          | thpb     | -             | 8.75<br>70     | -<br>-            | μs<br>CLK | 234 line             |

|         |                                     | прь      | <u>-</u><br>- | 9.63<br>77     | <del>-</del><br>- | μs<br>CLK | 240 line             |

|         | CLK-Hsync timing<br>hold/setup time | thch     | 10.0          | _              | _                 | ns        | _                    |

|         |                                     | thcs     | 10.0          | _              | -                 | ns        | _                    |

|         | V-Hsync timing<br>hold/setup time   | thvh     | 1             | -              | -                 | CLK       | _                    |

|         |                                     | thvs     | 10.0          | -              | -                 | ns        | _                    |

|         | Rise/fall                           | thrf     | -             | -              | 10.0              | ns        | _                    |

| VS      | Frequency                           | tv       | 15.85<br>–    | 16.68<br>262.5 | 17.51<br>–        | ms<br>H   | 59.94 Hz<br>(typ.)   |

|         | Display                             |          | -<br>-        | 14.87<br>234   | -<br>-            | ms<br>H   | 234 line             |

|         |                                     | tvd      | _             | 15.25<br>240   | -                 | ms<br>H   | 240 line             |

|         | Pulse-width                         | tvp      | 158.89<br>–   | 190.67<br>3    | -                 | μs<br>Η   | -                    |

|         | Pulse-width<br>+back-porch          | tvpb     | -<br>-        | 1.33<br>21     |                   | ms<br>H   | -                    |

|         | Rise/fall                           | tvrf     | -             | _              | 10.0              | ns        | -                    |

| Analog  | Setup time                          | tdas     | 10.0          | _              | -                 | ns        | _                    |

| R, G, B | Hold time                           | tdah     | 10.0          | _              | _                 | ns        | _                    |

**note 1**: In the display start period (pulse-width + back-porch), analog RGB signals should be blanking level.

# (4) mode: PAL, external CLK

|         | Parameter                         | Symbol   | min.        | typ.           | max.        | Unit      | Remarks              |

|---------|-----------------------------------|----------|-------------|----------------|-------------|-----------|----------------------|

| EXTCLK  | Frequency                         | 1 / tc   | –<br>118.75 | 8.0<br>125.00  | -<br>131.25 | MHz<br>ns | -                    |

|         | Rise/fall                         | terf     | -           | _              | 10          | ns        | -                    |

|         | Duty                              | tch / tc | 0.4         | 0.5            | 0.6         | -         | -                    |

| HS      | Frequency                         | th       | 60.80       | 64.00<br>512   | 67.20<br>–  | μs<br>CLK | 15.625 kHz<br>(typ.) |

|         | Display                           | thd      | -<br>-      | 40.00<br>320   |             | μs<br>CLK | -                    |

|         | Pulse-width                       | thp      | 1.0<br>_    | 4.7<br>38      | -           | μs<br>CLK | -                    |

|         | Pulse-width<br>+back-porch        | thnh     | -<br>-      | 9.63<br>77     | -<br>-      | μs<br>CLK | 234 line             |

|         |                                   | thpb     | -<br>-      | 10.25<br>82    | -           | μs<br>CLK | 240 line             |

|         | CLK-Hsync timing hold/setup time  | thch     | 10.0        | _              | _           | ns        | _                    |

|         |                                   | thcs     | 10.0        | _              | _           | ns        | _                    |

|         | V-Hsync timing<br>hold/setup time | thvh     | 1           | _              | _           | CLK       | _                    |

|         |                                   | thvs     | 10.0        | -              | _           | ns        | _                    |

|         | Rise/fall                         | thrf     | -           | _              | 10.0        | ns        | _                    |

| VS      | Frequency                         | tv       | 19.00<br>–  | 20.00<br>312.5 | 21.00<br>–  | ms<br>H   | 50.00 Hz<br>(typ.)   |

|         | Display                           |          | -<br>-      | 17.47<br>273   | -<br>-      | ms<br>H   | 234 line             |

|         |                                   | tvd      |             | 17.92<br>280   | -           | ms<br>H   | 240 line             |

|         | Pulse-width                       | tvp      | 153.60<br>- | 192.00<br>2.5  | -           | μs<br>Η   | -                    |

|         | Pulse-width<br>+back-porch        | tvpb     | -<br>-      | 1.86<br>29     | -           | ms<br>H   | 234 line             |

|         |                                   | τνρυ     | -           | 1.66<br>26     | -<br>-      | ms<br>H   | 240 line             |

|         | Rise/fall                         | tvrf     | -           | -              | 10.0        | ns        | _                    |

| Analog  | Setup time                        | tdas     | 10.0        | _              | _           | ns        | _                    |

| R, G, B | Hold time                         | tdah     | 10.0        | _              | _           | ns        | _                    |

**note 1**: In the display start period (pulse-width + back-porch), analog RGB signals should be blanking level.

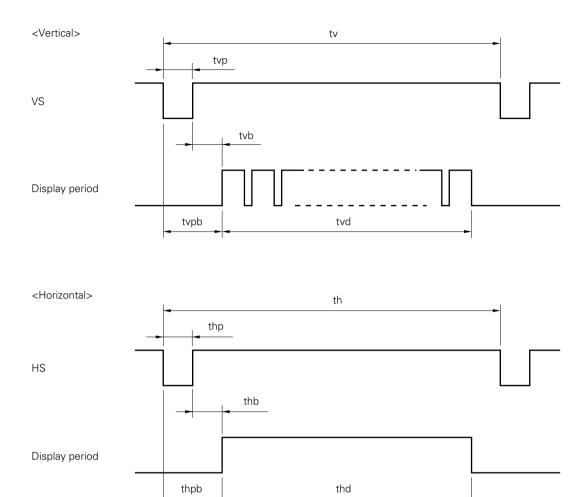

# **6.9 DEFINITION OF INPUT SIGNAL TIMING**

\* V  $_{\text{IH}} = 3.15$  V (min.) to 5.00 V (max.) V  $_{\text{IL}} = 0.00$  V (min.) to 0.90 V (max.)

<Luminance control signal >

Pulse A duty 100%: Relative luminance 100% Pulse A duty 20%: Relative luminance 10% (reference value)

A: 800  $\mu$ s to 3.7 ms B: 3.7 ms±10%

#### 7. GENERAL CAUTION

#### WARNING

Do not remove the rear case while the LCD module is operating, because dangerous high voltage is generating.

- (1) Caution when taking out the module

- 1 Pick the pouch only, when taking out module from a shipping package.

- (2) Cautions for handling the module

- 1 As the electrostatic discharges may break the LCD module, handle the LCD module with care. Peel a protection sheet off from the LCD panel surface as slowly as possible.

- ② As the LCD panel and back-light element are made from fragile glass material, impulse and pressure to the LCD module should be avoided.

- 3 As the surface of polarizer is very soft and easily scratched, use a soft dry cloth without chemicals for cleaning.

- 4 Do not pull the interface connectors in or out while the LCD module is operating.

- 5 Put the module display side down on a flat horizontal plane.

- 6 Handle connectors and cables with care.

- (3) Cautions for the operation

- ① When the module is operating, do not lose CLK, HS, or VS signals. If any one of these signals is lost, the LCD panel would be damaged.

- ② Obey the supply voltage sequence. If wrong sequence is applied, the module would be damaged.

- 3 Should not intermittently operate the module. It will be the cause of a short life.

- (4) Cautions for the atmosphere

- 1) Dew drop atmosphere should be avoided.

- ② Do not store and/or operate the LCD module in a high temperature and/or humidity atmosphere. Storage in an electro-conductive polymer packing pouch and under relatively low temperature atmosphere is recommended.

- 3 Backlight lamp tend to increase the turn on voltage in a cold atmosphere. And the life of module will become short.

- (5) Cautions for the module characteristics

- ① Do not apply fixed pattern data signal to the LCD module at product aging. Applying fixed pattern for a long time may cause image sticking.

- (6) Other cautions

- 1) Do not disassemble and/or re-assemble LCD module.

- 2 Do not re-adjust variable resistor or switch etc.

- 3 When returning the module for repair or etc., Please pack the module not to be broken. We recommend to use the original shipping packages.

Liquid Crystal Display has the following specific characteristics. There are not defects or malfunctions.

The display condition of LCD module may be affected by the ambient temperature.

The LCD module uses cold cathode tubes for backlighting. Optical characteristics, like luminance or uniformity, will change during time.

Uneven brightness and/or small spots may be noticed depending on different display patterns.

# **OUTLINE DRAWING (Unit in mm) Front view**

# **OUTLINE DRAWING (Unit in mm) Rear view**

No part of this document may be copied in any form or by any means without the prior written consent of NEC Corporation.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.