|                    | SPEC No.                             | MB1-1C102-056                                                             |

|--------------------|--------------------------------------|---------------------------------------------------------------------------|

| SHARP              | FILE No.                             |                                                                           |

| MOBILE LCD GROUP I | ISSUE                                | Sep,25,2009                                                               |

| SHARP CORPORATION  | PAGE                                 | 29 Pages                                                                  |

|                    | APPLICABLE                           | DIVISION                                                                  |

|                    | ■Mobile LC                           | CD DIVISION I                                                             |

|                    |                                      |                                                                           |

| SPECIFICATION      |                                      |                                                                           |

|                    | MOBILE LCD GROUP I SHARP CORPORATION | SHARP  MOBILE LCD GROUP I  SHARP CORPORATION  PAGE  APPLICABLE  Mobile LC |

DEVICE SPECIFICATION for TFT LCD Module Model No.

LS024J3LX01

SPEC No.

MODEL No.

MB1-1C102-056

LS024J3LX01

|             | PEGODDG OF DEVI                |             |         |

|-------------|--------------------------------|-------------|---------|

|             | RECORDS OF REV                 | ISION<br>T  |         |

| DATE        | REF.PAGE PARAGRAPH DRAWING No. | REVISED No. | SUMMARY |

| Sep.25.2009 |                                | V1.0        | release |

|             |                                |             |         |

|             |                                |             |         |

|             |                                |             |         |

| ·           |                                |             |         |

|             |                                |             |         |

|             |                                |             |         |

|             |                                |             |         |

|             |                                |             |         |

|             |                                |             |         |

|             |                                |             |         |

|             |                                |             |         |

|             |                                |             |         |

|             |                                |             |         |

|             |                                |             |         |

|             |                                |             |         |

|             |                                |             |         |

|             |                                |             |         |

|             |                                |             |         |

|             |                                |             |         |

|             |                                |             |         |

|             |                                | NOTICE      |         |

| SPEC No.      | MODEL No.   | PAGE |

|---------------|-------------|------|

| MB1-1C102-056 | LS024J3LX01 | 1    |

- o These specification sheets are the proprietary product of SHARP CORPORATION ("SHARP) and include materials protected under copyright of SHARP. Do not reproduce or cause any third party to reproduce them in any form or by any means, electronic or mechanical, for any purpose, in whole or in part, without the express written permission of SHARP.

- o The application examples in these specification sheets are provided to explain the representative applications of the device and are not intended to guarantee any industrial property right or other rights or license you to use them. SHARP assumes no responsibility for any problems related to any industrial property right of a third party resulting from the use of the device.

- The device listed in these specification sheets was designed and manufactured for use in Telecommunication equipment (terminals)

- o In case of using the device for applications such as control and safety equipment for transportation (aircraft, trains, automobiles, etc.), rescue and security equipment and various safety related equipment which require higher reliability and safety, take into consideration that appropriate measures such as fail-safe functions and redundant system design should be taken.

- o Do not use the device for equipment that requires an extreme level of reliability, such as aerospace applications, telecommunication equipment (trunk lines), nuclear power control equipment and medical or other equipment for life support.

- o SHARP assumes no responsibility for any damage resulting from the use of the device which does not comply with the instructions and the precautions specified in these specification sheets.

- o Contact and consult with a SHARP sales representative for any questions about this device.

#### [For handling and system design]

- (1) Do not scratch the surface of the polarizer film as it is easily damaged.

- (2) If the cleaning of the surface of the LCD panel is necessary, wipe it swiftly with cotton or other soft cloth. Do not use organic solvent as it damages polarizer.

- (3) Water droplets on polarizer must be wiped off immediately as they may cause color changes, or other defects if remained for a long time.

- (4) Since this LCD panel is made of thin glass, dropping the module or banging it against hard objects may cause cracks or fragmentation

- (5) Certain materials such as epoxy resin (amine's hardener) or silicone adhesive agent (de-alcohol or de-oxym) emits gas to which polarizer reacts (color change). Check carefully that gas from materials used in system housing or packaging do not hart polarizer.

- (6) Liquid crystal material will freeze below specified storage temperature range and it will not get back to normal quality even after temperature comes back within specified temperature range. Liquid crystal material will become isotropic above specified temperature range and may not get back to normal quality. Keep the LCD module always within specified temperature range.

- (7) Do not expose LCD module to the direct sunlight or to strong ultraviolet light for long time.

- (8) If the LCD driver IC (COG) is exposed to light, normal operation may be impeded. It is necessary to design so that the light is shut off when the LCD module is mounted.

- (9) Do not disassemble the LCD module as it may cause permanent damage.

| SPEC No.      | MODEL No.   | PAGE |

|---------------|-------------|------|

| MB1-1C102-056 | LS024J3LX01 | 2    |

(10) As this LCD module contains components sensitive to electrostatic discharge, be sure to follow the instructions in below.

#### ① Operators

Operators must wear anti-static wears to prevent electrostatic charge up to and discharge from human body.

#### ② Equipment and containers

Process equipment such as conveyer, soldering iron, working bench and containers may possibly generate electrostatic charge up and discharge. Equipment must be grounded through 100Mohms resistance. Use ion blower.

#### ③ Floor

Floor is an important part to leak static electricity which is generated from human body or equipment.

There is a possibility that the static electricity is charged to them without leakage in case of insulating floor, so the countermeasure(electrostatic earth:  $1 \times 10^8 \Omega$ ) should be made.

#### **4**Humidity

Proper humidity of working room may reduce the risk of electrostatic charge up and discharge. Humidity should be kept over 50% all the time.

#### ⑤Transportation/storage

Storage materials must be anti-static to prevent causing electrostatic discharge.

#### **6**Others

Protective film is attached on the surface of LCD panel to prevent scratches or other damages. When removing this protective film, remove it slowly under proper anti-ESD control such as ion blower.

- (11) Hold LCD very carefully when placing LCD module into the system housing. Do not apply excessive stress or pressure to LCD module. Do not to use chloroprene rubber as it may affect on the reliability of the electrical interconnection.

- (12) Do not hold or touch LCD panel to flex interconnection area as it may be damaged.

- (13) As the binding material between LCD panel and flex connector mentioned in 12) contains an organic material, any type of organic solvents are not allowed to be used. Direct contact by fingers is also prohibited.

- (14) When carrying the LCD module, place it on the tray to protect from mechanical damage. It is recommended to use the conductive trays to protect the CMOS components from electrostatic discharge. When holding the module, hold the Plastic Frame of LCD module so that the panel, COG and other electric parts are not damaged.

| İ | SPEC No.      | MODEL No.   | PAGE |

|---|---------------|-------------|------|

|   | MB1-1C102-056 | LS024J3LX01 | 3    |

- (15) Do not touch the COG's patterning area. Otherwise the circuit may be damaged.

- (16) Do not touch LSI chips as it may cause a trouble in the inner lead connection.

- (17) Place a protective cover on the LCD module to protect the glass panel from mechanical damages.

- (18) LCD panel is susceptible to mechanical stress and even the slightest stress will cause a color change in background. So make sure the LCD panel is placed on flat plane without any continuous twisting, bending or pushing stress.

- (19) Protective film is placed onto the surface of LCD panel when it is shipped from factory. Make sure to peel it off before assembling the LCD module into the system. Be very careful not to damage LCD module by electrostatic discharge when peeling off this protective film. Ion blower and ground strap are recommended.

- (20) Make sure the mechanical design of the system in which the LCD module will be assembled matches specified viewing angle of this LCD module.

- (21) This LCD module does not contain nor use any ODS (1,1,1-Trichloroethane, CCL4) in all materials used, in all production processes.

#### [For operating LCD module]

- (1) Do not operate or store the LCD module under outside of specified environmental conditions.

- (2) At the shipment, adjust the contrast of each LCD module with electric volume. LCD contrast may vary from panel to panel depending on variation of LCD power voltage from system.

- (3) As opt-electrical characteristics of LCD will be changed, dependent on the temperature, the confirmation of display quality and characteristics has to be done after temperature is set at 25 °C and it becomes stable.

#### [Precautions for Storage]

- (1) Do not expose the LCD module to direct sunlight or strong ultraviolet light for long periods. Store in a dark place.

- (2) The liquid crystal material will solidify if stored below the rated storage temperature and will become an isotropic liquid if stored above the rated storage temperature, and may not retain its original properties. Only store the module at normal temperature and humidity  $(25\pm5^{\circ}\text{C},60\pm10\%\text{RH})$  in order to avoid exposing the front polarizer to chronic humidity.

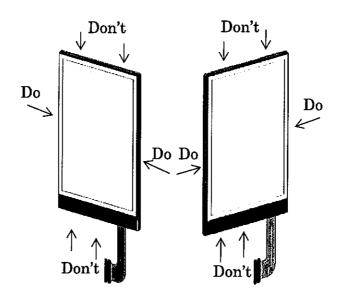

DO

(3) Keeping Method

**DON'T**

a. Don't keeping under the direct sunlight.

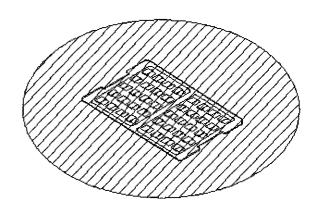

b. Keeping in the tray under the dark place.

| SPEC No.      | MODEL No.   | PAGE |

|---------------|-------------|------|

| MB1-1C102-056 | LS024J3LX01 | 4    |

- (1) Do not operate or store the LCD module under outside of specified environmental conditions.

- (2) Be sure to prevent light striking the chip surface.

#### [Other Notice]

- (1) Do not operate or store the LCD module under outside of specified environmental conditions.

- (2) As electrical impedance of power supply lines (VCC-VSS) are low when LCD module is working, place the de-coupling capacitor near by LCD module as close as possible.

- (3) Reset signal must be sent after power on to initialize LSI. LSI does not function properly until initialize it by reset signal.

- (4) Generally, at power on, in order not to apply DC charge directly to LCD panel, supply logic voltage first and initialize LSI logic function including polarity alternation. Then supply voltage for LCD bias. At power off, in order not to apply DC charge directly to LCD panel, execute Power OFF sequence and Discharge command.

- (5) Don't touch to PWB surface, exposed IC chip, electric parts and other parts, to any electric, metallic materials.

- (6) No bromide specific fire-retardant material is used in this module.

- (7) Do not display still picture on the display over 2 hours as this will damage the liquid crystal.

## [Precautions for Discarding Liquid Crystal Modules]

COG: After removing the LSI from the liquid crystal panel, dispose of it in a similar way to circuit boards from electronic devices.

LCD panel: Dispose of as glass waste. This LCD module contains no harmful substances. The liquid crystal panel contains no dangerous or harmful substances. The liquid crystal panel only contains an extremely small amount of liquid crystal (approx.100mg) and therefore it will not leak even if the panel should break,

-Its median lethal dose (LD50) is greater than 2,000 mg/kg and a mutagenetic (Aims test: negative) material is employed.

FPC: Dispose of as similar way to circuit board from electric device.

MB1-1C102-056

MODEL No.

LS024J3LX01

PAGE

5

## SHARP

| Contents                                                       | Page |

|----------------------------------------------------------------|------|

| 《Precautions》                                                  | 0    |

| 1. Application                                                 |      |

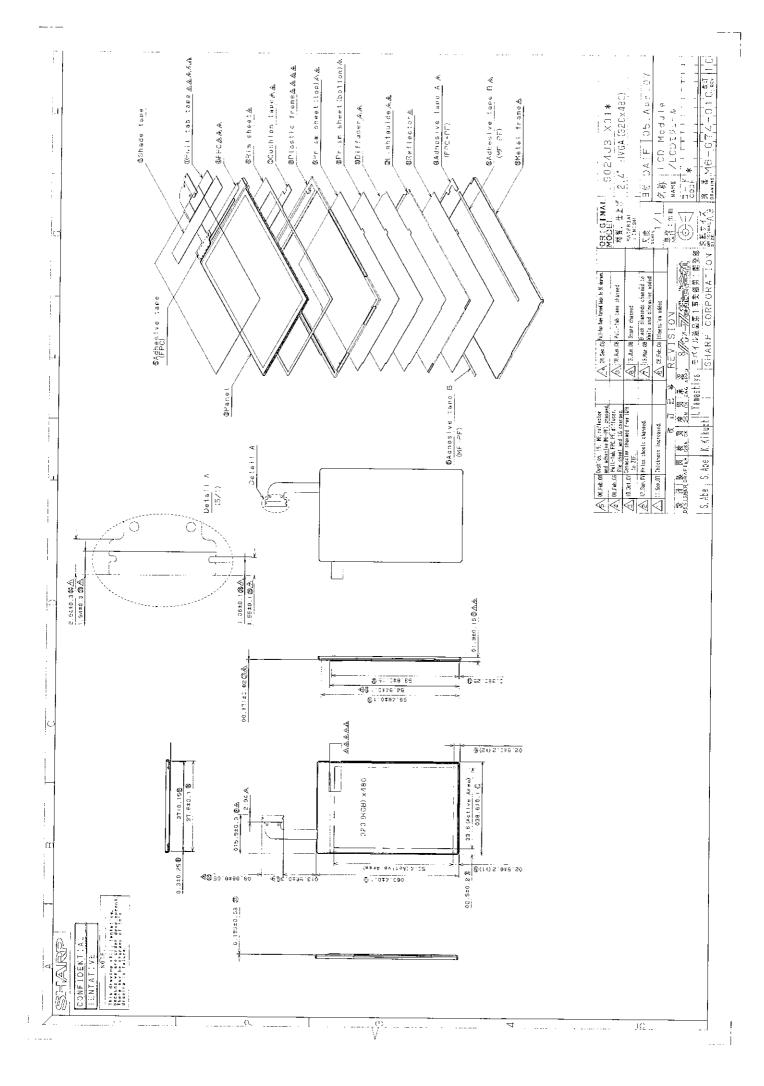

| 2. Construction and Outline                                    |      |

| 3. Mechanical specifications                                   |      |

| 4 Absolute maximum Ratings                                     |      |

| 4-1. Electrical absolute maximum ratings                       |      |

| 4-2. Environment Conditions                                    |      |

| 5. Electrical Specifications                                   |      |

| 5-1. Electrical characteristics                                |      |

| 5-2. LED back light                                            |      |

| 5-3. Interface signals                                         |      |

| 5-4. 3-wire 9bit Serial Interface Timing Diagrams              |      |

| 5-5. General Timing for LVDS Interface                         |      |

| 5-6. General Timing Diagram for RGB                            |      |

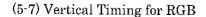

| 5-7. Vertical Timing for RGB                                   |      |

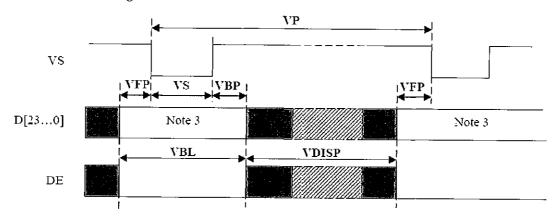

| 5-8. Horizontal Timing for RGB                                 |      |

| 5-9. /Reset Input Timing                                       |      |

| 5-10. Schematic of LCD module system                           |      |

| 6. Optical Characteristics                                     |      |

| 7. Command List                                                |      |

| 8. Initial Sequence                                            |      |

| 8-1. Case1-RESX line is held high or unstable by host at power |      |

| 8-2. Case2-RESX line is held low by host at power-on           |      |

| 8-3. Uncontrolled power-off                                    |      |

| 9. LCD module FPC Circuit diagram                              |      |

| 10. LCD module outline dimensions                              |      |

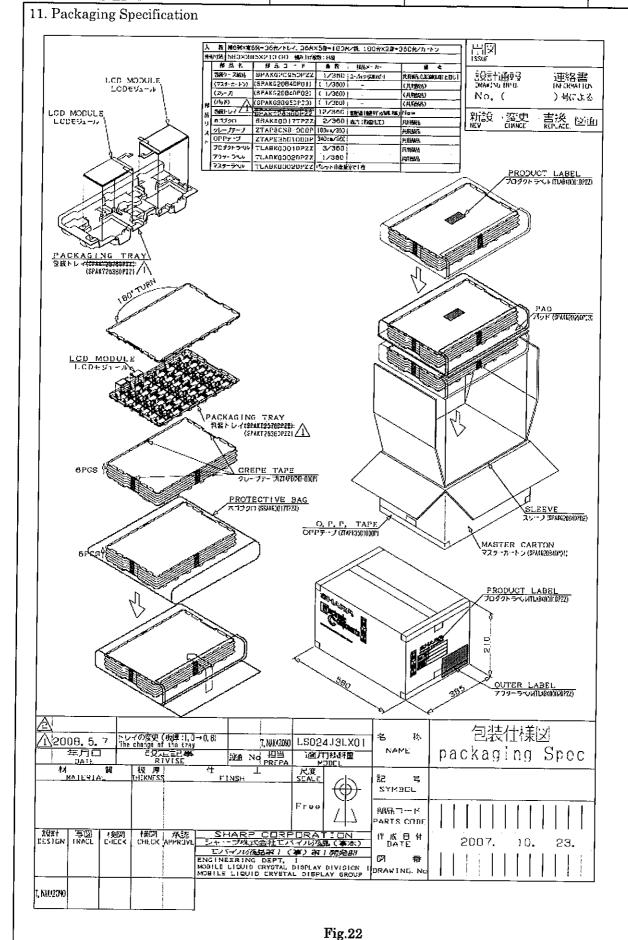

| 11. Packaging specification                                    |      |

|                                                                |      |

| SPEC No.      | MODEL No.   | PAGE |

|---------------|-------------|------|

| MB1-1C102-056 | LS024J3LX01 | 6    |

#### 1. Application

This data sheet is to introduce the specification of LS024J3LX01 active matrix 16,777,216 color LCD module.

Main color LCD module is controlled by Driver IC.

If any problem occurs concerning the items not stated in this specification, it must be solved sincerely by both parties after deliberation.

#### 2. Construction and Outline

Construction: LCD panel, Driver (COG), FPC with electric components,

4 White LED lump, prism sheet, diffuser, light guide and reflector, plastic frame to fix them mechanically.

Outline: See page 28 Connection: 24 pins;

There shall be no scratches, stains, chips, distortions and other external drawbacks that may affect the display function.

In order to realize thin module structure, double-sided adhesive tapes are used to fix LCD panels. As these tapes do not guarantee to permanently fix the panels, LCD panel may rise from the module when shipped from factory.

So please make sure to design the system to hold the edges of LCD panel by the soft material such as sponge

when LCD module is assembled into the cabinet.

#### 3. Mechanical Specification

Table 1

| Outline Dim       | ensions(typ)                   | 38.6(W)×60.4(H)×1.9(D) | mm |

|-------------------|--------------------------------|------------------------|----|

|                   | Active area                    | 33.60(W)×50.40(H)      | mm |

| Main LCD<br>Panel | Display format                 | 320(columns)×480(rows) | -  |

|                   | Dot pitch                      | 0.105(W)×0.105(H)      | mm |

|                   | Base color Notes Normaly black |                        |    |

| Mass              |                                | 9.3                    | g  |

#### Notes:

#### 1. Display module general parameters

| SPEC No.      | MODEL No.   | PAGE |

|---------------|-------------|------|

| MB1-1C102-056 | LS024J3LX01 | 7    |

4. Absolute Maximum Ratings

## (4·1) Electrical absolute maximum ratings

Table 2

| Parameter (requirement)      | Symbol           | Rating        | Unit |

|------------------------------|------------------|---------------|------|

| Power Supply Voltage (2.75V) | $V_{DD}$         | -0.3 to +3.5  | V    |

| Power Supply Voltage (1.8V)  | V <sub>DDI</sub> | -0.3 to +2.2  | V    |

| Logic Signal Input Voltage   | VI               | ·0.3 to +2.25 | V    |

| Logic Signal Output Voltage  | Vo               | -0.3 to +2.25 | V    |

#### (4-2) Environment Conditions

#### Table 3

| Item                | Т      | op    | Т      | stg   | D1              |

|---------------------|--------|-------|--------|-------|-----------------|

| rtent               | Min    | Max   | Min    | Max   | Remark          |

| Ambient temperature | -15℃   | +70°C | -30°C  | +80°C | Note2           |

| Humidity            | Note 1 |       | Note 1 |       | No condensation |

#### Notes:

1. Ta ≤ 40 °C......95 % RH Max

2. Ta > 40 °C......Absolute humidity shall be less than Ta=40 °C /95 % RH.

As opt-electrical characteristics of LCD will be changed, dependent on the temperature,

the confirmation of display quality and characteristics has to be done after temperature is set at 25 °C and it becomes stable. Be sure not to exceed the rated voltage, otherwise a malfunction may occur.

# SPEC No. MODEL No. PAGE MB1-1C102-056 LS024J3LX01 9

## **SHARP**

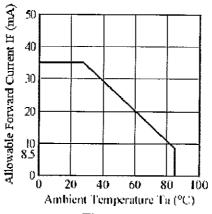

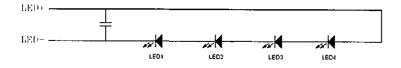

### (5-2) LED back light

At main panel the back light uses 4pcs edge light type white LED.

Table 5

|                                                | Tab        | Value     |     |      |  |

|------------------------------------------------|------------|-----------|-----|------|--|

| Item                                           | Min        | Nominal   | Max | Unit |  |

| Forward voltage (Vf) @ If                      | N/A        | 3.2       | 3.5 | V    |  |

| Forward current for LED (If)                   | -          | 18        | -   | mA   |  |

| Number of LED components                       | 4 pcs      | -1        |     |      |  |

| Connection type<br>(Serial / Parallel / Other) | All 4 LEDs | in Series |     |      |  |

## LED lamp: NSSW006

## Ambient Temperature vs. Allowable Forward Current

Fig.2

#### \*Schematics drawing of lighting

Fig.3

<sup>\*4</sup>pcs of LED

<sup>\*</sup>Please consider Allowable Forward Current on used temperature (refer to Ambient Temperature vs. Allowable Forward Current curve)

| SPEC No.      | MODEL No.     | PAGE |

|---------------|---------------|------|

| MB1-1C102-056 | LS024.131.X01 | 10   |

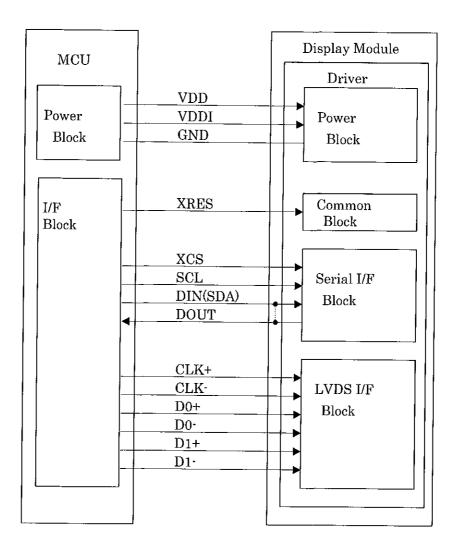

## (5-3) Interface signals

#### Table 6

| Pin No | Symbol | Description                       | I/O(1) | Remarks     |

|--------|--------|-----------------------------------|--------|-------------|

| 1      | TP     |                                   | -      | Tronici III |

| 2      | TP     |                                   | -      |             |

| 3      | XRES   | Reset                             | I      |             |

| 4      | XCS    | Chip Select                       | I      |             |

| 5      | SCL    | Clock                             | I      | -           |

| 6      | DIN    | Data In                           | I      |             |

| 7      | DOUT   | Data Out                          | 0      |             |

| 8      | GND    | Ground                            | -      | 0V          |

| 9      | ADDI   | Power supply for LCD              | -      | typ=1.8V    |

| 10     | VDD    | Power supply for LCD              | -      | typ=2.75V   |

| 11     | TED.   | Input current for LED components. | -      |             |

| 12     | LED+   | Input current for LED components. | -      | If=18mA     |

| 13     | GND    | Ground                            | •      | 0V          |

| 14     | D1+    | Data 1 channel+                   | I      |             |

| 15     | D1-    | Data 1 channel-                   | I      |             |

| 16     | GND    | Ground                            | -      | 0V          |

| 17     | CLK+   | Clock channel+                    | I      |             |

| 18     | CLK-   | Clock channel-                    | I      |             |

| 19     | GND    | Ground                            | -      | 0V          |

| 20     | D0+    | Data 0 channel+                   | I      |             |

| 21     | D0-    | Data 0 channel-                   | I      |             |

| 22     | GND    | Ground                            | -      | 0V          |

| 23     | TP     |                                   | -      |             |

| 24     | TP     |                                   | -      |             |

#### Notes:

1. The direction is named with respect to the display module, I = from host to module, O = from module to host.

|   | _ |  |

|---|---|--|

| _ | Δ |  |

|   |   |  |

| İ | SPEC No.      | MODEL No.   | PAGE |

|---|---------------|-------------|------|

|   | MB1·1C102-056 | LS024J3LX01 | 11   |

Table 7

| Assembled on | Item           | Description       |

|--------------|----------------|-------------------|

|              | Connector type | FPC LIF Connector |

| Dl DWD       | Pin amount     | 24                |

| Phone PWB    | Manufacturer   | JAE               |

|              | Part number    | CD002-1296-K126   |

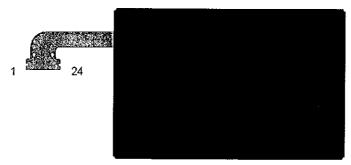

Connector pin layout of the display module is presented in Fig.4  $\,$

Fig.4 Connector pin layout of display module, bottom view of Module

MB1-1C102-056

LS024J3LX01

12

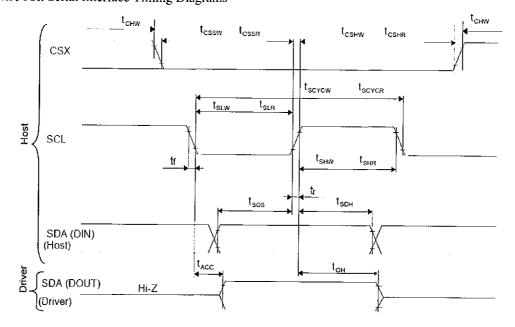

(5-4) 3-wire 9bit Serial Interface Timing Diagrams

SHARP

Fig.5 Table 8

| Table o                     |        |            |      |      |      |      |  |

|-----------------------------|--------|------------|------|------|------|------|--|

| Parameter                   | Symbol | Conditions | Min. | Тур. | Max. | Unit |  |

| Serial Clock Cycle(Write)   | tscycw | SCL        | 100  |      |      | ns   |  |

| SCL High pulse width(Write) | tshw   | SCL        | 35   |      |      | ns   |  |

| SCL Low pulse width(Write)  | tslw   | SCL        | 35   |      |      | ns   |  |

| Data setup time(Write)      | tsds   | SDA        | 30   |      |      | ns   |  |

| Data hold time(Write)       | tsdh   | SDA        | 30   |      |      | ns   |  |

| Serial Clock Cycle(Read)    | tscycr | SCL        | 150  |      |      | ns   |  |

| SCL High pulse width(Read)  | tshr   | SCL        | 60   |      |      | ns   |  |

| SCL Low pulse width(Read)   | tslr   | SCL        | 60   |      |      | ns   |  |

| Access time(1)              | tacc   | SDA        | 10   |      | 50   | ns   |  |

| Output disable time         | tон    | SDA        | 15   |      | 50   | ns   |  |

| CSX High pulse width        | tchw   | CSX        | 40   |      |      | ns   |  |

| CSX-SCL time(Write)         | tcssw  | CSX        | 30   |      |      | ns   |  |

|                             | tcshw  | CSX        | 30   |      |      | ns   |  |

| CSX-SCL time(Read)          | tcssr  | CSX        | 60   |      |      | ns   |  |

|                             | tcshr  | CSX        | 60   |      |      | ns   |  |

- 1. Ta = -30 +70 °C, VDDI=1.65V-1.95 V, VDD= 2.3-2.9V, VSS=0V

- 2. The output signal's rise and fall times are stipulated to be from TBD to 15 ns.

- 3. The input signal's rise and fall times (tf, tr) are stipulated to be equal to or less than 15ns.

Fig.6

MB1-1C102-056

MODEL No.

0223110.

LS024J3LX01

PAGE

13

SHARP.

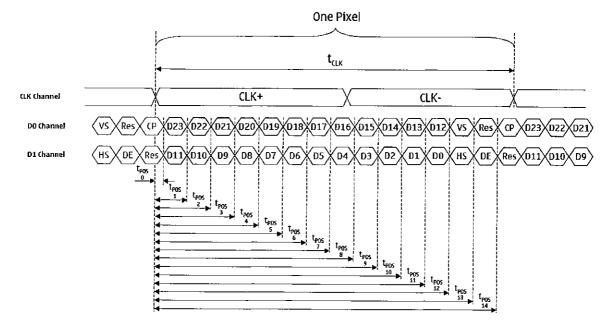

### (5-5) General Timing for LVDS Interface

Table 9

| Item                              | Symbol                  | Min.                     | Тур.                      | Max.                     | Unit |  |  |  |

|-----------------------------------|-------------------------|--------------------------|---------------------------|--------------------------|------|--|--|--|

| Pixel Clock Frequency             | PCLK                    | 8.0                      |                           | 11.4                     | MHz  |  |  |  |

| Pixel Clock Cycle                 | tclk                    | 87.7                     |                           | 125.0                    | ns   |  |  |  |

| Clock-to-Clock Position Jitter    | t <sub>CL</sub> Kjitter | 0                        |                           | 300                      | ps   |  |  |  |

| Clock-to-Data Position Jitter     | t <sub>DATAjitter</sub> | 0                        |                           | 330                      | ps   |  |  |  |

| Ideal t <sub>pos0</sub> Position  | t <sub>pos0</sub>       | 0                        | 0                         | 0                        | ns   |  |  |  |

| Ideal tpost Position              | tposi                   | (1/15)*t <sub>CLK</sub>  | (1/15)*t <sub>el.K</sub>  | (1/15)*t <sub>CLK</sub>  | ns   |  |  |  |

| Ideal t <sub>pos2</sub> Position  | tpos2                   | (2/15)*t <sub>CLK</sub>  | (2/15)*t <sub>CLK</sub>   | (2/15)*t <sub>CLK</sub>  | ns   |  |  |  |

| Ideal tpost Position              | ${ m t_{pos3}}$         | (3/15)*t <sub>CLK</sub>  | (3/15)*t <sub>CLK</sub>   | (3/15)*t <sub>CLK</sub>  | ns   |  |  |  |

| Ideal tpost Position              | t <sub>pos4</sub>       | (4/15)*t <sub>CLK</sub>  | (4/15)*t <sub>CLK</sub>   | (4/15)*t <sub>CLK</sub>  | ns   |  |  |  |

| Ideal tpos5 Position              | t <sub>posā</sub>       | (5/15)*t <sub>CLK</sub>  | (5/15)*t <sub>CLK</sub>   | (5/15)*t <sub>CLK</sub>  | ns   |  |  |  |

| Ideal tpos6 Position              | tpos6                   | (6/15)*t <sub>CLK</sub>  | (6/15)*t <sub>CLK</sub>   | (6/15)*t <sub>CLK</sub>  | ns   |  |  |  |

| Ideal t <sub>pos7</sub> Position  | t <sub>pos7</sub>       | (7/15)*t <sub>CLK</sub>  | (7/15)*t <sub>CLK</sub>   | (7/15)*t <sub>CLK</sub>  | ns   |  |  |  |

| Ideal tpos8 Position              | t <sub>pos8</sub>       | (8/15)*t <sub>CLK</sub>  | (8/15)*t <sub>CLK</sub>   | (8/15)*t <sub>CLK</sub>  | ns   |  |  |  |

| Ideal t <sub>pos9</sub> Position  | t <sub>pos9</sub>       | (9/15)*t <sub>CLK</sub>  | (9/15)*t <sub>CLK</sub>   | (9/15)*t <sub>CLK</sub>  | ns   |  |  |  |

| Ideal tposto Position             | t <sub>pos10</sub>      | (10/15)*t <sub>CLK</sub> | (10/15)*t <sub>CLK</sub>  | (10/15)*t <sub>CLK</sub> | ns   |  |  |  |

| Ideal tpos11 Position             | t <sub>pos11</sub>      | (11/15)*t <sub>CLK</sub> | (11/15)*t <sub>el.k</sub> | (11/15)*t <sub>CLK</sub> | ns   |  |  |  |

| Ideal tpos12 Position             | tpos12                  | (12/15)*t <sub>CLK</sub> | (12/15)*t <sub>CLK</sub>  | (12/15)*t <sub>CLK</sub> | ns   |  |  |  |

| Ideal t <sub>post3</sub> Position | tpos13                  | (13/15)*t <sub>CLK</sub> | (13/15)*t <sub>CLK</sub>  | (13/15)*t <sub>CLK</sub> | ns   |  |  |  |

| Ideal tpos14 Position             | t <sub>pos14</sub>      | (14/15)*tcl.k            | (14/15)*t <sub>CLK</sub>  | (14/15)*t <sub>CLK</sub> | ns   |  |  |  |

Notes:

1. Ta = -30 to 70 °C (to +85 °C no damage), VDDI = 1.65 - 1.95V, VSS (DGND) = 0V

Fig.7

MB1-1C102-056

SPEC No.

MODEL No.

LS024J3LX01

PAGE

14

Fig.8

| SPEC No. |  |

|----------|--|

MODEL No.

LS024J3LX01

PAGE

15

SHARP

MB1-1C102-056 LS02

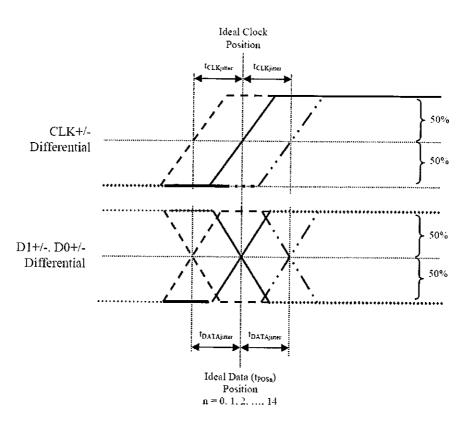

(5-6) General Timing Diagram for RGB

Vertical Sync.

Fig.9

| SPEC No. |  |

|----------|--|

| 1        |  |

MODEL No.

PAGE

MB1-1C102-056

LS024J3LX01

8

## 5. Electrical Specifications

SHARP.

## (5-1) Electrical characteristics

Table 4

| Parameter(re                                                 | quirement)                     | Condition                       | Symbol               | 5                            | Specificati | on                   | Unit      |

|--------------------------------------------------------------|--------------------------------|---------------------------------|----------------------|------------------------------|-------------|----------------------|-----------|

|                                                              |                                |                                 |                      | min                          | typ         | max                  | 1         |

| Power Supply                                                 | Voltage                        | Operating Voltage               | V <sub>DD</sub>      | 2.6                          | 2.75        | 2.90                 | v         |

|                                                              | Voltage (logic)                | I/O Supply Voltage              | $V_{ m DDI}$         | 1.65                         | 1.8         | 1.95                 | V         |

| Logic High Level Input Voltage                               |                                | IN= -10uA                       | V <sub>IH</sub>      | $0.7V_{\mathrm{DDI}}$        | -           | VDDI                 | V         |

|                                                              | el Input Voltage               | IN= -+0uA                       | V <sub>IL</sub>      | 0.0                          | -           | 0.3 V <sub>DDI</sub> | V         |

| Logic High Le                                                | vel Output Voltage             | $I_{OUT} = -1 mA$               | V <sub>OH</sub>      | $0.8\mathrm{V}_\mathrm{DDI}$ | -           | VDDI                 | V         |

|                                                              | el Output Voltage              | $I_{OUT} = +1 mA$               | Vol                  | 0.0                          |             | 0.2 V <sub>DDI</sub> | V         |

|                                                              | put Voltage for Clock          | CLK+/-                          | VDIFCLK              | 87.5                         | 100         | 200                  | mV        |

|                                                              | put Voltage for Data           | D0+/-, D1+/-                    | VDIFDATA             | 87.5                         | 100         | 200                  | mV        |

|                                                              | Mode Voltage for Clock         | CLK+/-                          | VCMCLK               | 0.6                          | 0.9         | 1.2                  | V         |

|                                                              | Mode Voltage for Data          | D0+/-, D1+/-                    | V <sub>CMDATA</sub>  | 0.6                          | 0.9         | 1.2                  | V         |

| Differential Input Low Level<br>Threshold Voltage for Clock  |                                | CLK+/-                          | VTHLCLK              | ·40                          | -           | -                    | mV        |

| Differential Input High Level<br>Threshold Voltage for Clock |                                | CLK+/-                          | VTHHCLK              | -                            | -           | 40                   | mV        |

| Differential In<br>Threshold Volt                            |                                | D0+/-, D1+/-                    | VTHLDATA             | -40                          | -           | -                    | mΫ        |

| Differential In<br>Threshold Volt                            | put High Level<br>age for Data | D0+/-, D1+/-                    | V <sub>THHDATA</sub> | -                            | -           | 40                   | mV        |

| Differential Te                                              | rmination Resistor             | CLK+/-, D0+/-, D1+/-            | RTERM                | 80                           | 100         | 120                  | $ \Omega$ |

| Self Bias Resis                                              | tor                            | CLK+/-, D0+/-, D1+/-            | RSELFBIAS            | -                            |             | 50                   | kΩ        |

| Logic High Lev                                               | el Leakage                     | ·                               | Ilih                 | -                            |             | 1                    | uA        |

| Logic Low Leve                                               | el Leakage                     |                                 | Ilrl                 | <u></u>                      | -           | -                    | uA        |

| Input Leakage                                                | Current +                      | CLK+, D0+, D1+                  | I <sub>IN+</sub>     | -                            | -           | 90                   | uA        |

| Input Leakage                                                | Current -                      | CLK-, D0-, D1-                  | I <sub>IN</sub> -    | -90                          | -           | -                    | uA        |

|                                                              |                                |                                 | IDDI                 | -                            | 1.0         | -                    | mA        |

|                                                              | Partial Mode off Idle Mode off | All pixels white <sup>(1)</sup> | IDD                  |                              | 11.2        |                      | mA        |

| Current                                                      | Sleep Out Mode                 | A11 ' 1 11 1/1                  | IDDI                 | -                            | 1.0         | -                    | mA        |

| Consumption                                                  | orceb out mode                 | All pixels black <sup>(1)</sup> | IDD                  |                              | 8.0         | •                    | mA        |

| 1                                                            | Sleep In Mode                  | N/A <sup>(1)</sup>              | IDDI                 | -                            | 0.04        | -                    | mA        |

|                                                              | breep in mode                  | IV/A···                         | IDD                  |                              | 0.005       |                      | mA        |

#### Notes:

1. Conditions: Ta = 25°C, VDD = 2.75V, VDDI = 1.8V,Refresh rate=60Hz.

Ambient temperature,Ta = -15°C to +70°C operational

Measurement Point

MB1-1C102-056

SPEC No.

LS024J3LX01

16

## SHARP

Fig.10 Table 10

| <u>Item</u>               | Symbol | Conditions | Min. | Typ. | Max. | Unit |

|---------------------------|--------|------------|------|------|------|------|

| Vertical cycle            | VP     |            | 486  |      | 490  | line |

| Vertical low pulse width  | VS     |            | 2    |      | 4    | line |

| Vertical front porch      | VFP    |            | 2    |      | 4    | line |

| Vertical back porch       | VBP    |            | 2    |      | 4    | line |

| Vertical data start point |        | VS+VBP     | 4    |      | 8    | line |

| Vertical blanking period  | VBL    | VFP+VS+VBP | 6    |      | 10   | line |

| Vertical active area      |        | VDISP      |      | 480  |      | line |

| Vertical Refresh Rate     | VRR    |            | 50   |      | 65   | Hz   |

- 1. Ta = -30 +70°C, VDDI = 1.65 1.95 V, VDD = 2.3 2.9 V, VSS = 0 V

- 2. Signal rise and fall times are equal or less than 20 ns.

- 3. Measuring of input signals are using  $0.30 \times \text{VDDI}$  for low state and  $0.70 \times \text{VDDI}$  for high state.

- 4. Data lines can be set to "High" or "Low" during blanking time Don't care.

MB1-1C102-056

LS024J3LX01

17

## (5-8) Horizontal Timing for RGB

SHARP

Fig.11 Table 11

| Item                                          | Symbol | Conditions        | Min. | Тур. | Max. | Unit |

|-----------------------------------------------|--------|-------------------|------|------|------|------|

| HS cycle                                      | HP     |                   | 352  |      | 528  | PCLK |

| HS low Pulse width                            | HS     |                   | 2    |      | 256  | PCLK |

| Horizontal back porch                         | НВР    |                   | 2    |      | 256  | PCLK |

| Horizontal front porch                        | HFP    |                   | 2    |      | 256  | PCLK |

| Horizontal data start point                   |        | HS+HBP            | 30   |      | 206  | PCLK |

| Horizontal blanking period                    | HBLK   | HFP+HS+HBP        | 32   |      | 208  | PCLK |

| Horizontal active area                        | HDISP  |                   |      | 320  |      | PCLK |

| Pixel clock frequency When RGB I/F is running | PCLK   | VRR=50Hz~<br>60Hz | 8.0  |      | 11.4 | MHz  |

- 1. Ta = -30 · +70°C, VDDI = 1.65 1.95 V, VDD = 2.3 2.9 V, VSS = 0 V

- 2. Signal rise and fall times are equal or less than 20 ns.

- 3. Measuring of input signals are using  $0.30 \times VDDI$  for low state and  $0.70 \times VDDI$  for high state.

- 4. HP is multiples of eight PCLK.

- 5. Data lines can be set to "High" or "Low" during blanking time Don't care.

LS024J3LX01

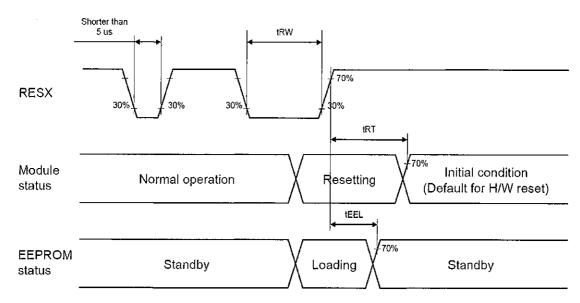

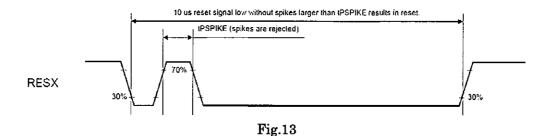

## (5-9) /Reset Input Timing

Fig.12

Table 12

| Parameter         | Symbol | Condition  | Sp  | ecification |       | Unit |

|-------------------|--------|------------|-----|-------------|-------|------|

|                   |        |            | Min | Тур         | Max   |      |

| Reset pulse width | tRW    | Note 3,4   | 10  |             |       | us   |

| Reset time        | tRT    | Note 1,2,5 |     |             | 5,120 | ms   |

| EEPROM load time  | tEEL   | Note 1     |     |             | 5     | ms   |

#### Notes:

- 1. tRT includes the time required to load initialization data from EEPROM.

- 2. The display is blanked following the falling edge of RESX and continues to remain blank during tRT.

Since the initial condition is 'Sleep In', 'Display OFF', the display will in face remain blank until 'Sleep Out', 'Display ON' commands are received.

- 3. False trigger rejection applies to RESX.

- 4. Noise spike rejection applies to RESX.(See Fig.13, tPSPIKE= Max20ns)

- 5.5mS in 'Sleep In' mode, 120mS in 'Sleep Out' mode.

| SI | 4 | Δ | D | D |

|----|---|---|---|---|

| SPEC No.      | MODEL No.   | PAGE |

|---------------|-------------|------|

| MB1-1C102-056 | LS024J3LX01 | 19   |

(5·10) Schematic of LCD module system

Fig.14

MB1-1C102-056

MODEL No.

LS024J3LX01

PAGE

20

## SHARP

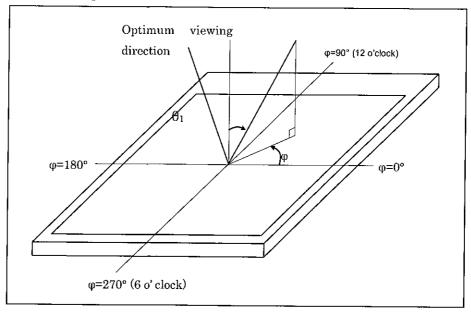

## 6. Optical Characteristics

Table 13

|               |               | ıa                  | Die 13 |       |              |

|---------------|---------------|---------------------|--------|-------|--------------|

| Parameter     | Symbol        | Condition           | Тур    | Unit  | Remark       |

| Brightness    | $\mathbf{Br}$ | θ <sub>1</sub> =0°  | 370    | cd/m² | Note 1, 2    |

| Contrast      | Co            | θ <sub>1</sub> =0°  | 540    | -     | Note 1, 2, 3 |

| Viewing Angle | φ=0°          | θ <sub>1</sub> =15° | 190    | -     | Note 1, 2, 3 |

| (Contrast)    | φ=90°         |                     | 190    | j<br> |              |

|               | φ=180°        |                     | 210    |       |              |

|               | φ=270°        |                     | 215    |       |              |

|               | φ=0°          | θ <sub>1</sub> =30° | 60     | -     | Note 1, 2, 3 |

|               | φ=90°         |                     | 65     |       |              |

|               | φ=180°        |                     | 65     |       |              |

|               | φ=270°        |                     | 70     |       |              |

|               | φ=0°          | θ <sub>1</sub> =45° | 30     | -     | Note 1, 2, 3 |

|               | φ=90°         |                     | 30     |       |              |

|               | φ=180°        |                     | 30     |       |              |

|               | φ=270°        |                     | 35     |       |              |

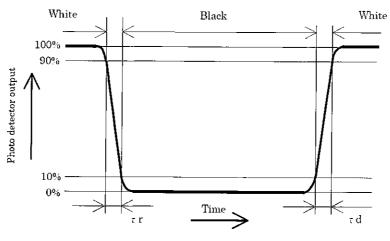

| Response Time | tr1           | θ <sub>1</sub> =0°  | 7      | ms    | Note 4       |

|               | tr2           |                     | 15     |       |              |

| White         | u'            | θ1=0°               | 0.185  | -     | -            |

| Chromaticity  | v'            |                     | 0.464  |       |              |

| NTSC ratio    | -             | θ <sub>1</sub> =0°  | 81     | %     |              |

<sup>\*</sup>VDD=2.75,Ta = 25°C

MB1-1C102-056

LS024J3LX01

21

#### Notes:

1. Definition of range of visual angle

Fig.15

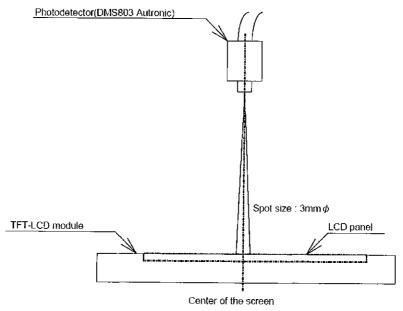

2. Brightness is measured as follows, and is defined as the brightness of all pixels "White" at the center of display area on optimum contrast.

Fig. 16

3. Contrast ratio is defined as follows:

Co= Luminance(brightness) all pixcels "White"

Luminance(brightness) all pixcels "Black"

| SPEC No. |  |

|----------|--|

|          |  |

MODEL No.

PAGE

22

LS024J3LX01

SHARP

MB1-1C102-056 L

4. Response time is defined as follows:

Fig. 17

MODEL No.

LS024J3LX01

PAGE

23

SHARP.

#### 7. Command List

#### Table 14

MB1-1C102-056

| Op-code<br>(Hex)(1) | Mnemonic  | Function                                  | Type <sup>(4)</sup> |

|---------------------|-----------|-------------------------------------------|---------------------|

| 00                  | NOP       | No operation                              | C+0                 |

| 01                  | SWRESET   | Software Reset                            | C+0                 |

| 04                  | RDDIDIF   | Read display ID information(3)            | R+d3                |

| 05                  | RDNUMPE   | Read Number of ParityErrors(3)            | R+1                 |

| 06                  | RDRED     | Read Red colour <sup>(3)</sup>            | R+1                 |

| 07                  | RDGREEN   | Read Green colour <sup>(3)</sup>          | R+1                 |

| 08                  | RDBLUE    | Read Blue colour <sup>(3)</sup>           | R+1                 |

| 09                  | RDDST     | Read display status(3)                    | R+d4                |

| 0A                  | RDDPM     | Read Display Power Mode <sup>(3)</sup>    | R+1                 |

| 0B                  | RDDMADCTL | Read Display MADCTL(3)                    | R+1                 |

| 0C                  | RDDCOLMOD | Read Display Pixel Format(3)              | R+1                 |

| 0D                  | RDDIM     | Read Display Image Mode <sup>(3)</sup>    | R+1                 |

| 0E                  | RDDSM     | Read Display Signal Mode <sup>(3)</sup>   | R+1                 |

| 0F                  | RDDSDR    | Read Display Self Diagnostic Result       | R+1                 |

| 10                  | SLPIN     | Sleep In <sup>(3)</sup>                   | C+0                 |

| 11                  | SLPOUT    | Sleep Out                                 | C+0                 |

| 12                  | PTLON     | Partial mode on <sup>(3)</sup>            | C+0                 |

| 13                  | NORON     | Normal mode on <sup>(3)</sup>             | C+0                 |

| 26                  | GAMSET    | Gamma set <sup>(3)</sup>                  | W+1                 |

| 28                  | DSPOFF    | Display off(3)                            | C+0                 |

| 29                  | DSPON     | Display on <sup>(3)</sup>                 | C+0                 |

| 2A                  | CASET     | Column address set                        | W+4                 |

| 2B                  | PASET     | Page address set                          | W+4                 |

| 2C                  | RAMWR     | Memory write                              | W+n                 |

| 30                  | PLTAR     | Partial area <sup>(3)</sup>               | W+4                 |

| 36                  | MADCTL    | Memory data access control <sup>(3)</sup> | W+1                 |

| B0 to D9            |           | Reserved <sup>(2)</sup>                   |                     |

| DA                  | RDID1     | Read ID1 <sup>(3)</sup>                   | R+1                 |

| DB                  | RDID2     | Read ID2 <sup>(3)</sup>                   | R+1                 |

| DC                  | RDID3     | Read ID3 <sup>(3)</sup>                   | R+1                 |

| DE to FF            | -         | Reserved <sup>(2)</sup>                   |                     |

- 1. Undefined commands are treated as NOP (00h) command.

- 2. B0h to D9h and DEh to FFh are defined by Sharp. Before shipping, and by agreement with Sharp, these commands can be made available to the customer. By default these commands operate as NOP.

- 3: Commands which affect the displayed image, (10h, 12h, 13h, 26h, 28h, 29h, 30h and 36h), take effect during the Vertical sync pulse when the display module is in 'Sleep Out' mode to avoid abnormal visual effects. During 'Sleep In' mode, these commands take effect immediately. Read commands, (04h, 05h, 06h, 07h, 08h, 09h, 0Ah, 0Bh, 0Ch, 0Dh, 0Eh, DAh, DBh, DCh), are updated immediately both in 'Sleep In' mode and 'Sleep Out' Mode.

- 4. C=command, W=write, R=read, +=number of following parameters, (in Bytes), d=dummy clock cycle.

| SPEC No.      | MODEL No.   | PAGE |

|---------------|-------------|------|

| MB1-1C102-056 | LS024J3LX01 | 24   |

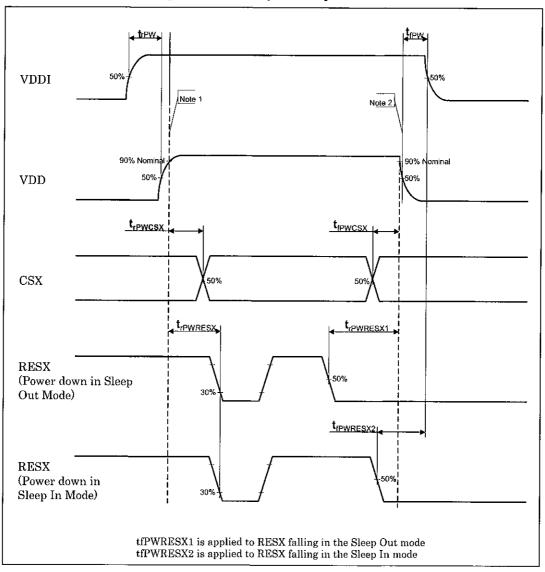

#### 8. Initial Sequence

During power on, 'RESX' must be applied for a minimum of 10us after both VDD and VDDI have been applied. 'RESX' can be undefined during power-on but must be applied subsequently to ensure correct LCD controller operation. VDDI and VDD can be applied in any order.

During power-off, if the LCD controller is in 'Sleep Out' mode, VDD and VDDI must be powered down a minimum of 120ms after RESX has been released. If the LCD controller is in 'Sleep In' mode, VDDI and VDD can be powered down a minimum of 0ms after 'RESX' has been released. VDDI and VDD can be powered down in any order.

'CSX' can be applied at any time. 'RESX' has priority over 'CSX'.

#### (8.1) Case 1 · RESX line is held high or unstable by host at power-on

Fig.18

- 1. Time when the latter signal rises up to 90% of its <u>typical</u> value, e.g. when VDD comes later. This time is defined at the cross point of 90% of 2.75V, not 2.3V.

- 2. Time when the former signal falls down to 90% of its  $\underline{\text{typical}}$  value, e.g. when VDD falls earlier. This time is defined at the cross point of 90% of 2.75V, not 2.3V.

MODEL No.

LS024J3LX01

PAGE

25

SHARP

Table 15

MB1-1C102-056

| Parameter | Value        |

|-----------|--------------|

| trPW      | +/- no limit |

| tfPW      | +/- no limit |

| trPWCSX   | +/- no limit |

| tfPWCSX   | +/- no limit |

| trPWRESX  | + no limit   |

| tfPWRESX1 | min 120mS    |

| tfPWRESX2 | + no limit   |

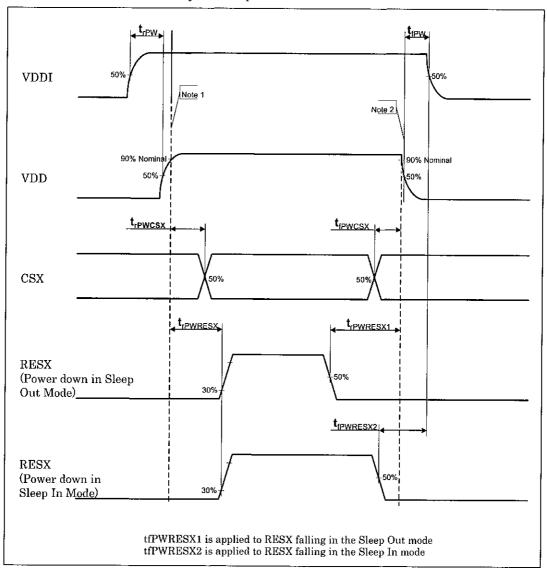

#### (8.2) Case 2 - RESX line is held low by host at power-on

Fig.19

- 1. Time when the latter signal rises up to 90% of its <u>typical</u> value, e.g. when VDD comes later. This time is defined at the cross point of 90% of 2.75V, not 2.3V.

- 2. Time when the former signal falls down to 90% of its <u>typical</u> value, e.g. when VDD falls earlier. This time is defined at the cross point of 90% of 2.75V, not 2.3V.

MODEL No.

**PAGE**

MB1-1C102-056

LS024J3LX01

26

#### SHARP

Table 16

| Parameter | Value        |

|-----------|--------------|

| trPW      | +/- no limit |

| tfPW      | +/- no limit |

| trPWCSX   | +/- no limit |

| tfPWCSX   | +/- no limit |

| trPWRESX  | min 10 us    |

| tfPWRESX1 | min 120mS    |

| tfPWRESX2 | min 0mS      |

#### Notes:

There will be no damage to the display module if the above power sequences are not met.

There will be no abnormal visible effects on the display panel during the sequence.

There will be no abnormal visible effects on the display between the end of power on sequence and before entering Sleep Out mode. Also between entering Sleep In mode and power off sequence.

There are no limits for RESX timings during power on sequence. (e.g. from the undefined level to high or low, when the first RESX low pulse after VDD and VDDI are powered-on, etc.)

#### (8.3) Uncontrolled power-off

Uncontrolled power-off (e.g. the battery is removed without following the proper power-off sequence), will not damage the LCD module or cause the LCD module to inflict any damage on the host. If the LCD module is currently displaying an image, this image may persist for some time. The image will fade however as the LC pixels naturally discharge. Although difficult to predict, the time taken for the discharge process is maximum 10 seconds. Once the LC pixels are fully discharged, the display will appear to be blank.

MODEL No.

PAGE

MB1-1C102-056

LS024J3LX01

27

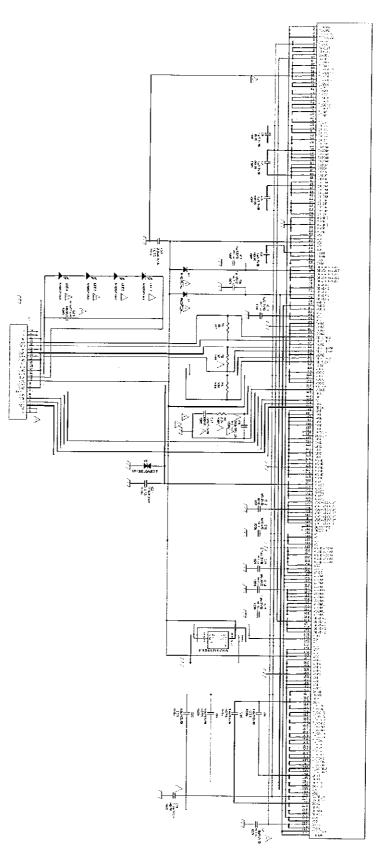

## 9. LCD module FPC Circuit diagram

SHARP

Fig.20

MODEL No.

-----

PAGE

SHARP

MB1-1C102-056 LS0243

LS024J3LX01

29