|   |                        |                                 | Date : Novembe |

|---|------------------------|---------------------------------|----------------|

|   | SPE                    | CIFICATIONS                     |                |

|   | Product Name           | ACX450AK                        | N-7            |

| A | ccepted by :<br>Date : |                                 |                |

|   |                        | n Display Inc.<br>the Shimegard | 2              |

| D/            | wision History                      | Product<br>Name | ACX450AKN-7 |           |

|---------------|-------------------------------------|-----------------|-------------|-----------|

|               | Revision History                    |                 |             |           |

| Date          | Contents of change                  | R               | easons      | Remarks   |

| Aug. 8, 2012  | Release                             |                 |             | Version 1 |

| Aug. 31, 2012 | (A) Add Inspection spec.            |                 |             | Version 2 |

| Nov.21 , 2012 | (A)Packing Spec.<br>(C)Product Name |                 |             | Version 3 |

| Nov.27 , 2012 | (A)MODULE ID                        |                 |             | Version 4 |

| (C): Changed  | (A): Appended (D): Deleted (F       | F): Filled in   |             |           |

# CONTENTS

| 1.   | BASIC SPECIFICATIONS                        | 1            |

|------|---------------------------------------------|--------------|

| 1.1  | STRUCTURES                                  | 1            |

| 1.2  | BLOCK DIAGRAM                               | 2            |

| 1.3  |                                             |              |

| 1.4  |                                             |              |

| 1.5  | INSTRUCTION OF DIFFERENT DIRECTION SCANNING | 4            |

| 2.   | ELECTRICAL SPECIFICATION                    |              |

| 2.1  |                                             | -            |

| 2.2  | MIPI INTERFACE CHARACTERISTICS              | 6            |

| 2.3  |                                             |              |

| 2.4  |                                             |              |

| 2.5  |                                             |              |

| 2.6  | COMMAND TABLE                               | 46           |

| 2.7  |                                             |              |

| 2.8  |                                             |              |

| 3.   | ABSOLUTE MAXIMUM RATINGS                    |              |

| 4.   | OPTICAL CHARACTERISTICS                     |              |

| 4.1  |                                             |              |

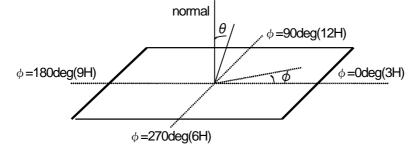

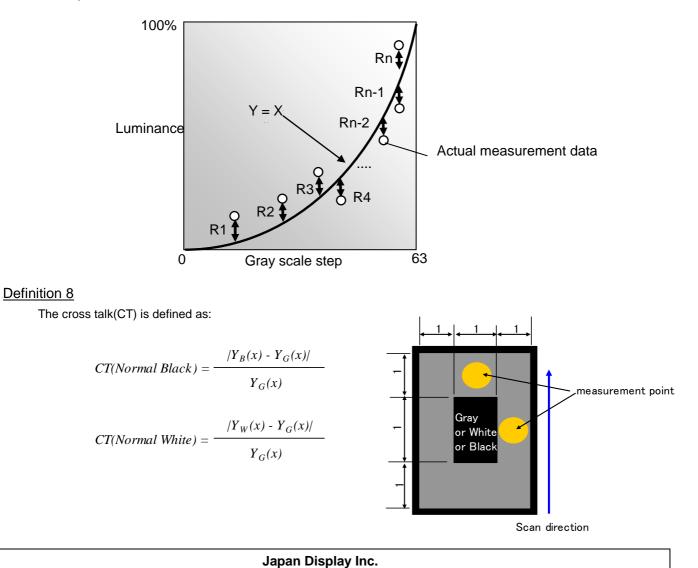

| 4.2  | DEFINITIONS AND MEASUREMENT CONDITIONS      | 51           |

| 5.   | INSPECTION STANDARD                         |              |

| 5.1  |                                             |              |

| 5.2  |                                             |              |

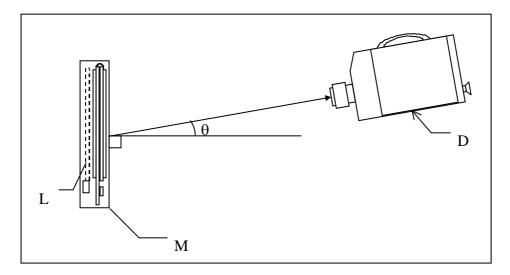

| 5.3  | INSPECTION CONDITION                        | 55           |

| 5.4  |                                             |              |

| 5.5  |                                             |              |

| 6.   | WARRANTY                                    |              |

| 7.   | RELIABILITY                                 |              |

| 7.1  |                                             |              |

| 7.2  |                                             |              |

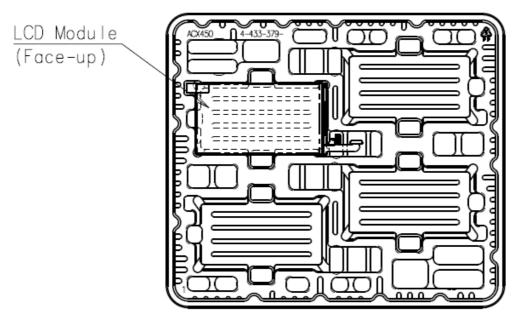

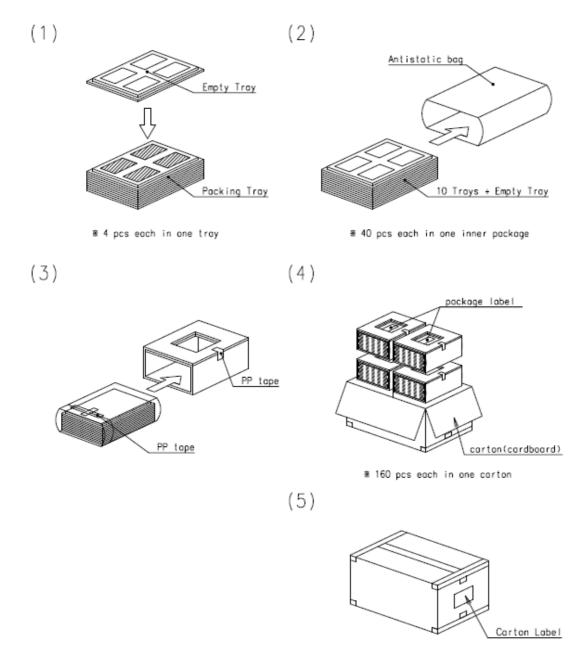

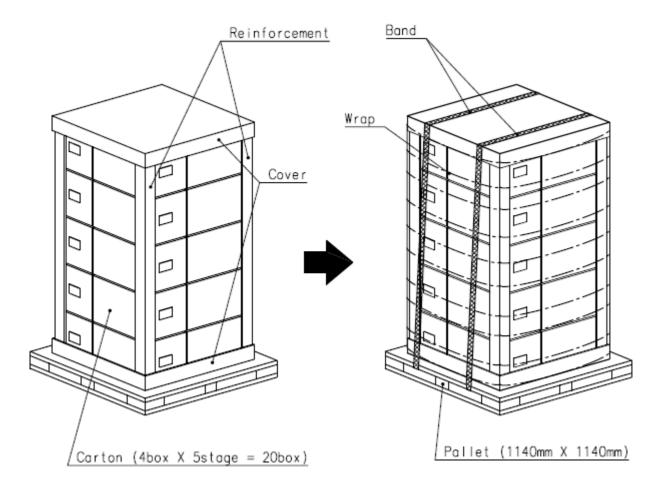

| 8.   | PACKING SPECIFICATIONS                      | 59           |

| 8.1  | LCM TRAY                                    | 59           |

| 8.2  |                                             |              |

|      | PALLET                                      |              |

|      | MODULE ID                                   |              |

| 9.   | LCD MODULE USAGE AND PRECAUTION             |              |

| 9.1  |                                             |              |

| 9.2  | ASSEMBLY PRECAUTIONS                        | 64           |

| 9.3  |                                             |              |

| 9.4  | DISASSEMBLY AND MODIFICATION                | 65           |

| 9.5  |                                             |              |

| 9.6  | DISPOSAL                                    | 66           |

| 9.7  | OTHERS                                      | 66           |

| 10.  | CHANGES                                     | 66           |

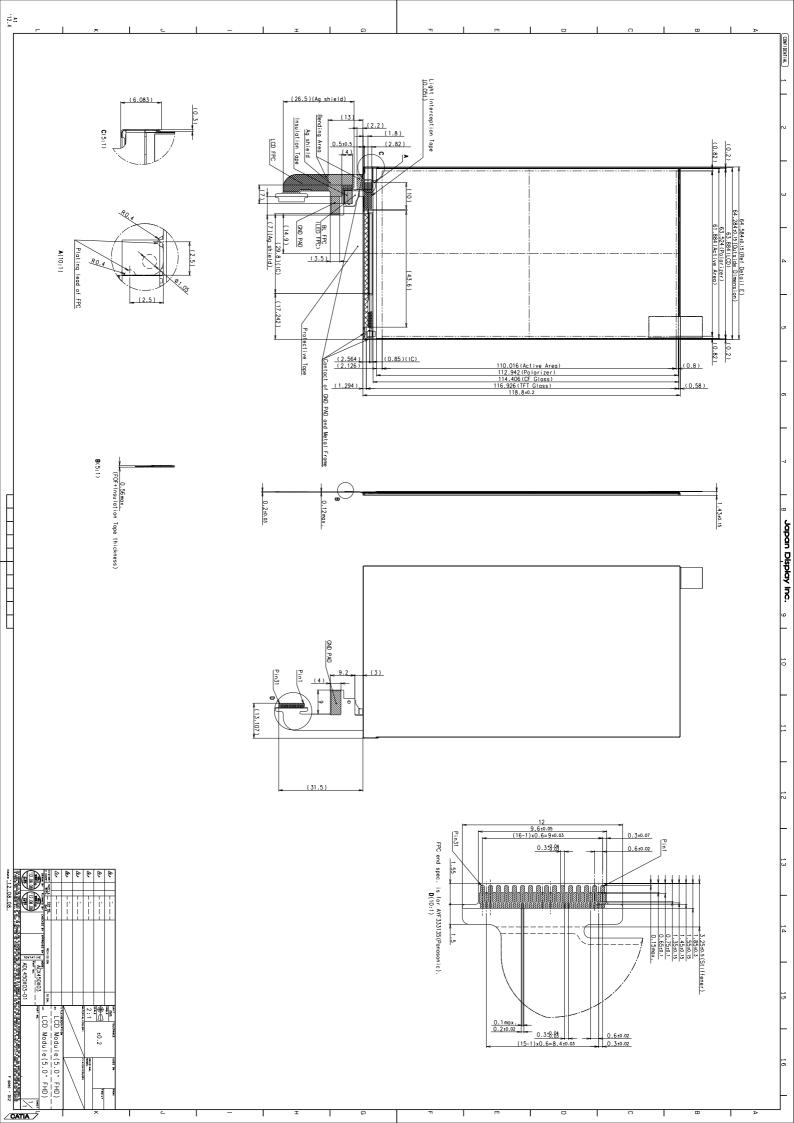

| Ουτι | LINE DRAWING                                | tached sheet |

# 1. BASIC SPECIFICATIONS

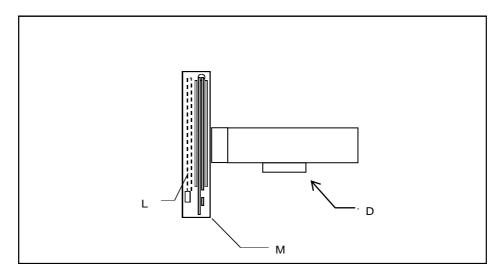

# 1.1 STRUCTURES

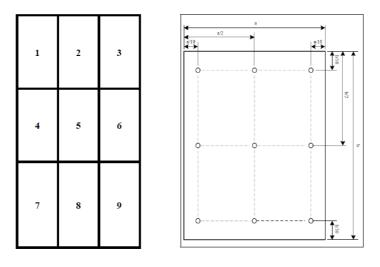

| No | Parameter         | Specifications                                                                 |

|----|-------------------|--------------------------------------------------------------------------------|

| 1  | LCD Structure     | 4.97" Low Temperature Poly-Silicon TFT                                         |

|    |                   | of DC-Vcom driving method with Pixel Column inversion                          |

| 2  | Outward           | 64.284 (W) x 118.8 (H) x 1.43 (D) [mm] (excluding FPC and parts of protruding) |

| 3  | Weight            | (21.2) [g]                                                                     |

| 4  | Screen Size       | 61.884 × 110.016 [mm]                                                          |

| 5  | Number of Dots    | 1080 x RGB (W) x 1920 (H)                                                      |

| 6  | Dot Pitch         | 0.0191 (W) x 0.0573 (H) [mm]                                                   |

| 7  | Color Layout      | RGB vertical stripe                                                            |

| 8  | Viewing Direction | Wide viewing angle                                                             |

| 9  | LCD Optical Mode  | Normally Black                                                                 |

| 10 | Polarizer Type    | Hard coat treating (3H)                                                        |

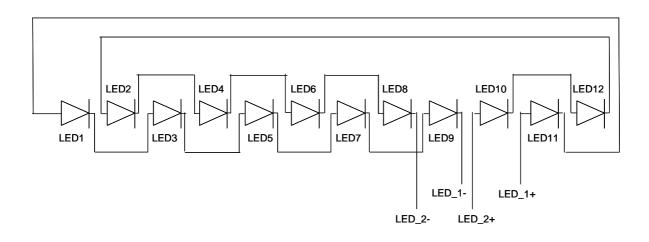

| 11 | Light Source Type | Back light with white LEDs (12chips)                                           |

| 12 | Number of Colors  | 16M (24bits)                                                                   |

| 13 | Frame Rate        | 55~60Hz(recommend)                                                             |

| 14 | LCM type          | Transmissive                                                                   |

| 15 | Driving Method    | DC Vcom                                                                        |

| 16 | Driving inversion | Pixel Column inversion                                                         |

| 17 | Page orientation  | Portrait mode                                                                  |

| 18 | Outline dimension | See 2D drawing                                                                 |

| 19 | System Interface  | MIPI DSI 4data lanes and 1clock lane                                           |

|    | Version           | MIPI DSI: Version 1.01.00r11                                                   |

|    |                   | MIPI D-PHY: Version 1.00.00                                                    |

|    |                   | MIPI DCS: Version 1.01.00                                                      |

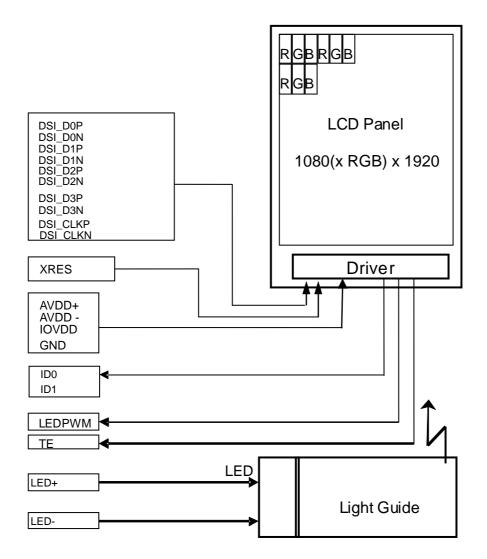

#### 1.2 BLOCK DIAGRAM

LED B/L CIRCUIT

## 1.3 INTERFACE PINS

| Pin No | Symbol   | Function                           | I/O | Remarks                       |

|--------|----------|------------------------------------|-----|-------------------------------|

| 1      | LED_1+   | LED Power Supply                   | -   | Anode                         |

| 2      | LED_2+   | LED Power Supply                   | -   | Anode                         |

| 3      | LED_1-   | LED Power Supply                   |     | Cathode                       |

| 4      | LED_2-   | LED Power Supply                   |     | Cathode                       |

| 5      | NC       |                                    |     | Not Connected (keep floating) |

| 6      | GND      | Ground                             | -   |                               |

| 7      | TE       | TE signal output from driver IC    | 0   |                               |

| 8      | NC       | -                                  | -   | Not Connected (keep floating) |

| 9      | IOVDD    | Power Supply for I/O               | -   |                               |

| 10     | AVDD+    | Power Supply for Analog            | -   |                               |

| 11     | AVDD-    | Power Supply for Analog            |     |                               |

| 12     | LEDPWM   | Backlight LED driver PWM           | 0   |                               |

| 13     | XRES     | Device Reset Signal                | I   |                               |

| 14     | ID0      | ID0 (100kΩpull-up to IOVDD)        | 0   | ID0=1                         |

| 15     | ID1      | ID1 (100kΩpull-up to IOVDD)        | 0   | ID1=1                         |

| 16     | GND      | Ground                             |     |                               |

| 17     | DSI_D2P  | 3rd MIPI data positive signal      | I   |                               |

| 18     | DSI_D2N  | 3rd MIPI data negative signal      | I   |                               |

| 19     | GND      | Ground                             |     |                               |

| 20     | DSI_D1P  | 2nd Lane MIPI data positive signal | I   |                               |

| 21     | DSI_D1N  | 2nd Lane MIPI data negative signal | I   |                               |

| 22     | GND      | Ground                             | -   |                               |

| 23     | DSI_CLKP | MIPI Clock positive signal         | I   |                               |

| 24     | DSI_CLKN | MIPI Clock negative signal         | I   |                               |

| 25     | GND      | Ground                             |     |                               |

| 26     | DSI_D0P  | 1st Lane MIPI data positive signal | I/O |                               |

| 27     | DSI_DON  | 1st Lane MIPI data negative signal | I/O |                               |

| 28     | GND      | Ground                             |     |                               |

| 29     | DSI_D3P  | 4th Lane MIPI data positive signal | I   |                               |

| 30     | DSI_D3N  | 4th Lane MIPI data negative signal | I   |                               |

| 31     | GND      | Ground                             |     |                               |

| Product Number    | ACX450AKN-7 | <b>Revision Number</b> | 04 | Page 4/66  |

|-------------------|-------------|------------------------|----|------------|

| i loudot i tumboi |             |                        | 01 | i ago i/oo |

The use of ACX450AKM-7 basically conforms to specifications of LCD driver IC:R63311 (Renesas ). It explains typical function in this manual.

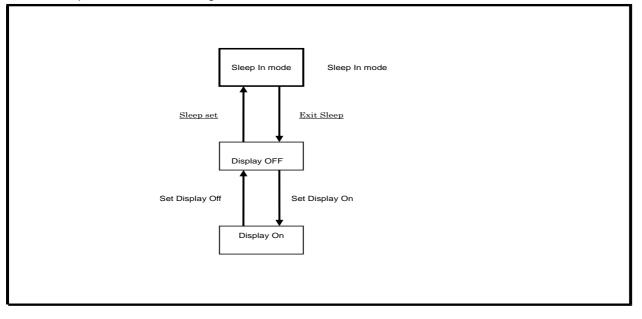

# 1.4 BASIC OPERATION MODE

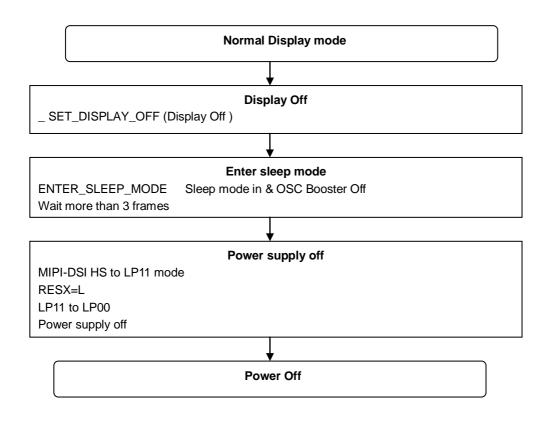

The basic operation mode of ACX450AKM is illustrated below. When changing from one mode to another, make sure to follow the sequence indicated in the figure.

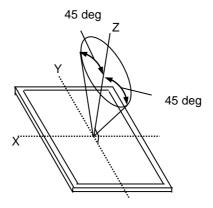

# 1.5 INSTRUCTION OF DIFFERENT DIRECTION SCANNING

# 2. ELECTRICAL SPECIFICATION

# 2.1 DC SPECIFICATION

|                           |         |                 | GND=0V, Am  | bient temperature | e = 25°C unless ot | therwise | specified. |

|---------------------------|---------|-----------------|-------------|-------------------|--------------------|----------|------------|

| Deremeter                 | Symphol | Condition       |             | Ratings           |                    | Unit     | Pins       |

| Parameter                 | Symbol  | Condition       | Min.        | Тур.              | Max.               | Unit     | (Main FPC) |

|                           | AVDD+   |                 | 4.75        | 5.0               | 5.25               | V        |            |

| Power Supply Voltage      | AVDD-   |                 | -4.75       | -5.0              | -5.25              | V        |            |

|                           | IOVDD   |                 | 1.65        | 1.8               | 1.95               | V        |            |

| Low-level input voltage   | VIL     |                 | GND         | -                 | 0.3 x IOVDD        | V        | 13         |

| High-level input voltage  | VIH     |                 | 0.7 x IOVDD | -                 | IOVDD              | V        | 13         |

| Low-level output voltage  | VOL     | IOL=+1.0mA      | GND         | -                 | 0.2 x IOVDD        | V        | 7,8,12     |

| High-level output voltage | VOH     | IOH=-1.0mA      | 0.8 x IOVDD | -                 | IOVDD              | V        | 7,8,12     |

| Input leak current        | ILI     |                 |             |                   | 10                 | μA       |            |

| Power supply current      | IAVDD+  | White           |             | 10.9              | (16.2)             | mA       |            |

| (RMS) Note.2, Note.3      |         | Black           |             | 8.9               | (13.7)             | mA       |            |

|                           |         | Color Bar note5 |             | 11.2              | (16.1)             | mA       |            |

|                           | IAVDD-  | White           | (-12.7)     | -7.4              |                    | mA       |            |

|                           |         | Black           | (-10.9)     | -6.2              |                    | mA       |            |

|                           |         | Color Bar note5 | (-13.2)     | -8.2              |                    | mA       |            |

|                           | IIOVDD  | White           |             | 17.2              | (23.5)             | mA       |            |

|                           |         | Black           |             | 17.1              | (23.4)             | mA       |            |

|                           |         | Color Bar note5 |             | 18.6              | (25.2)             | mA       |            |

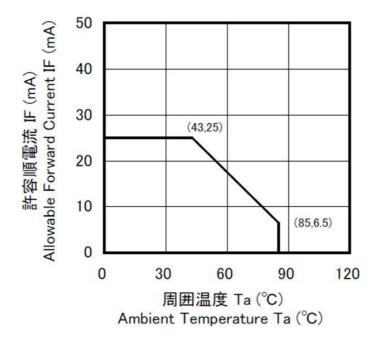

| LED forward current       | IF      |                 |             | 20                | 25                 | mA       |            |

| LED VF                    | VF      | 1LED, IF=20mA   |             | 3.0               | 3.3                | V        |            |

## <Note>

1) Rated values indicate operating range of electrical functions.

Typ. values are at the condition of power supply voltage is Typ., the ambient temperature is 25°C, still display image.

Max. values are at the condition of power supply voltage is in a range of "DC SPECIFICATIONS", ambient temperature is in a range of operating temperature, still display image.

3) The state of MIPI is Video mode and 60Hz frame rate.

4) Power supply current "color bar" is the full screen color bar still display.

# 2.2 MIPI INTERFACE CHARACTERISTICS

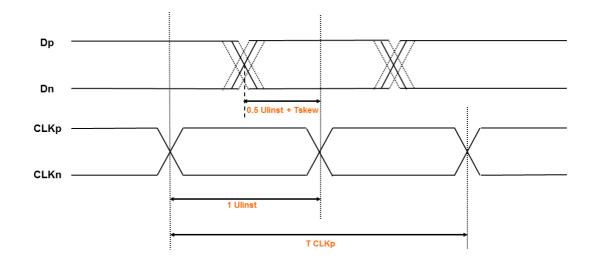

# 2.2.1 High Speed Data Transmission

| Parameter                                       | Symbol    | min   | typ | max   | Units  | Notes |

|-------------------------------------------------|-----------|-------|-----|-------|--------|-------|

| UI instantaneous                                | Ulinst    | (1)   |     | 5     | ns     |       |

| Data to Clock Skew<br>[Measured at transmitter] | Tskew[TX] | -0.15 |     | +0.15 | Ulinst |       |

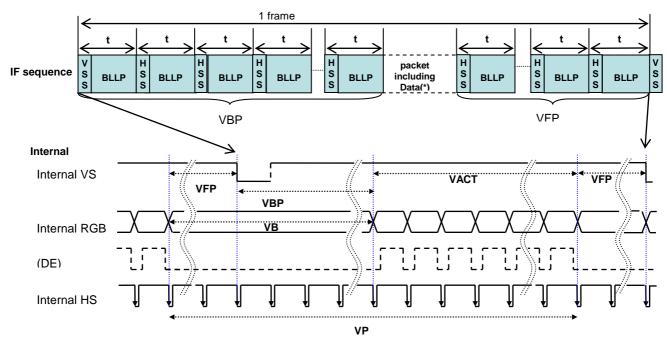

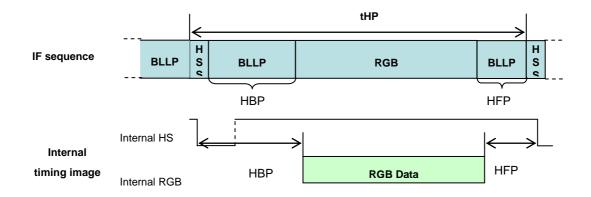

# 2.3 FRAME RATE SPECIFICATION

In case of video mode, Input Horizontal frequency MUST NOT be over Minimum value including OSC variation. So please keep input specification as follows;

|                                           | Column inversion |      |       |       |

|-------------------------------------------|------------------|------|-------|-------|

| Item                                      | Min.             | Тур. | Max.  | unit  |

| Horizontal Active Number                  |                  | 1080 |       | dots  |

| Vertical Active Number                    |                  | 1920 |       |       |

| Vertical Cycle (VP)                       | 1928             |      |       | lines |

| Vertical Blanking(VBL)                    | 8                |      |       | lines |

| Vertical front porch(VFP)                 | 3                |      |       | lines |

| Vertical Back porch(VBP)                  | 5                |      |       | lines |

| Horizontal Frequency<br>(internal timing) |                  |      | 135.8 | kHz   |

| Vertical Frequency                        | 55(TBD)          |      | 60    | Hz    |

Note: Video Mode Max. 60.0Hz has already considered IC CLK tolerance +/- 5% VBL=VBP+VFP

#### 2.4 MIPI-DSI INTERFACE

#### 2.4.1 System Interface Configuration

The DSI incorporated in the LCD driver complies with the following standards.

MIPI DSI: Version 1.01.00r11 MIPI D-PHY: Version 1.00.00 MIPI DCS: Version 1.01.00

#### 2.4.2 Introduction

The module DSI interface employs clock and 4 data lanes.

-DSI-D0+,D0-is bi-directional with Low-Power Reverse Escape Mode supporting Low Power Data Transmission.

-DSI-D1+,D1-,D2+,D2-,D3+,D3- is unidirectional without Turnaround or any kind of Reverse communication functionality.

The DSI interface can communicate in 2 modes, Low Power Data Transmission Mode (LP-Mode) and High Speed Mode (HS-Mode).

In LP-Mode, the differential pair lines are operating in Single End Mode, the differential receiver is disabled and the termination resistor is disconnected from the differential pair lines.

In HS-Mode, the termination resistor is connected and the differential pairs are no longer working in Single End mode.

The lane states are determined by the active Transmitter (Tx). In Normal operation, the lanes are being driven by either a High Speed Transmitter (HS-Tx) or a Low Speed Transmitter (LP-Tx). In HS mode, there are 2 possible lane states and in Low Speed mode, there are 4 possible lanes states defined by the table below:-

| State | Line Voltage Levels |          | High Speed (HS)  | Low-Po       | wer (LP)    |

|-------|---------------------|----------|------------------|--------------|-------------|

| Code  | Dx+ line            | Dx- line | Burst Mode       | Control Mode | Escape Mode |

| HS-0  | HS-Low              | HS-High  | Differential – 0 | Note 1       | Note 1      |

| HS-1  | HS-High             | HS-Low   | Differential – 1 | Note 1       | Note 1      |

| LP-00 | LP-Low              | LP-Low   | N/A              | Bridge       | Space       |

| LP-01 | LP-Low              | LP-High  | N/A              | HS-Request   | Mark-0      |

| LP-10 | LP-High             | LP-Low   | N/A              | LP-Request   | Mark-1      |

| LP-11 | LP-High             | LP-High  | N/A              | Stop         | Note 2      |

Notes:-

1. During High Speed Transmission, the Low-Power Receivers constantly check for LP-00 state code.

2. If LP-11 occurs during Escape mode, the Lane will return to Stop State (Control Mode LP-11)

#### 2.4.3 Video mode

ACX450 driver supports only Video Mode. There are thee formats of transmission packet sequences. ACX450 supports two of these formats. See the following formats.

| Image Transmission packet sequence            | implementation |

|-----------------------------------------------|----------------|

| Video mode ( Non-burst mode with sync pulses) | Not supported  |

| Video mode (Non-burst mode with sync events)  | Supported      |

| Video mode (Burst mode with sync events)      | Supported      |

| Command mode                                  | Not supported  |

Clock lane should support only continuous clock.

## Vertical Video Mode timing ( Non-Burst Mode with sync Events / Burst Mode )

VSS: Vsync Start packet, HSS: Hsync Start packet , BLLP: Blanking packet or Low Power Mode , RGB data: Packed pixel stream (RGB data) packet Horizontal Video mode timing ( Non-Burst Mode with sync Events / Burst Mode )

## 2.4.4 DSI Clock Lanes

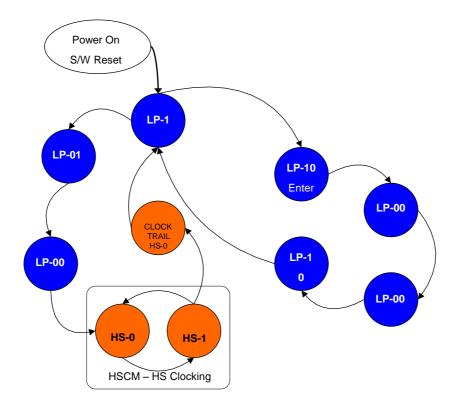

The DSI Clock Lanes can operate in different power modes, controlled by the Transmitter (Tx):-

- High Speed Clock Mode (HSCM)

It is only possible to enter High Speed Clock Mode (HSCM) from Low Power Mode (LPM) by the sequence LPM → LP-01

$\rightarrow$  LP-00  $\rightarrow$  HS-0  $\rightarrow$  HS-0/1 (HSCM).

- Low Power Mode (LPM)

There are 3 possible methods to enter Low Power mode (LPM).

- 1. Power On, Software Reset or Hardware Reset  $\rightarrow$  LPM.

- 2. From Ultra Low Power Mode (ULPM) by the sequence ULPM  $\rightarrow$  LP-10  $\rightarrow$  LP-11 (LPM).

- 3. From High Speed Clock Mode (HSCM) by the sequence HSCM  $\rightarrow$  HS-0  $\rightarrow$  LP-11 (LPM)

- Ultra Low Power Mode. (ULPM)

It is only possible to enter Ultra Low Power Mode (ULPM) from Low Power Mode (LPM) by the sequence LPM  $\rightarrow$  LP-10  $\rightarrow$  LP-00 (ULPM).

The protocols for entering/leaving the different power modes can be summarized by the following diagram:-

## Figure 1 – Clock Lane Power Modes.

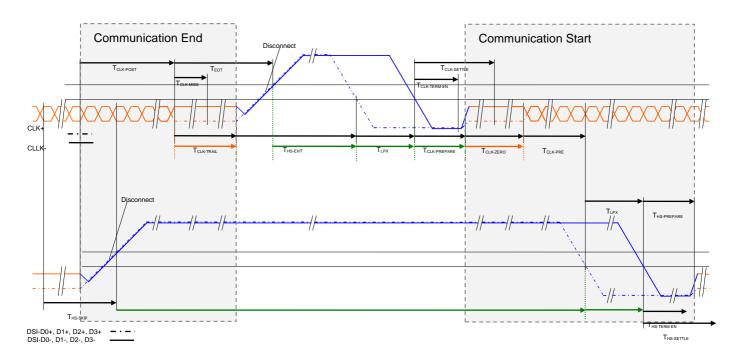

For a high speed communication, the DSI CLK+/- lines are always started before high speed data is sent on DSI-D0+/- or DSI D1+/- or DSI D2+/- or DSI D3+/-. The clock lines also continue clocking for a defined period after the data transmission has ended as shown in the diagram below.

Figure 2 – Clock Lane Power Transitions.

The High Speed Clock burst always starts and ends with state HS-0 so the burst always contains an even number of clock transitions.

## 2.4.5 DSI Data Lanes.

## 2.4.5.1 Introduction

The DSI Data Lanes DSI D0+/-, D1+/-, D2+/- and D3+/- can operate in different modes, controlled by the Transmitter (Tx):-

- High Speed Data Transmission (HSDT) where the display is receiving data from the host.

It is only possible to enter High Speed Data Transmission (HSDT) from Control Mode by the sequence LP-11  $\rightarrow$  LP-01  $\rightarrow$  LP-00  $\rightarrow$  HS-0  $\rightarrow$  HS-0/1 (HSDT).

- Escape Mode – Applies only to D0+/-.

- Bus Turnaround Mode - Applies only to D0+/-.

It is only possible to enter Bus Turnaround Mode from Control Mode by the sequence LP-11  $\rightarrow$  LP-10  $\rightarrow$  LP-00  $\rightarrow$  LP-10  $\rightarrow$  LP-00.

Control Mode is defined as the Data Lane Stop State LP-11.

## 2.4.5.2 High Speed Data Transmission

All High Speed Data Transmissions start and end with a Stop State (LP-11). The DSI CLK+/- lanes have already entered High Speed Clock Mode before starting High Speed Data Transmission.

A burst of High Speed Data always has an integer number of bytes with a minimum length of one byte.

High Speed Data Transmission can be started and ended independently for any data Lane, however normally the data Lanes will start synchronously but may end at different times if there are an unequal number of transmitted bytes for each Lane.

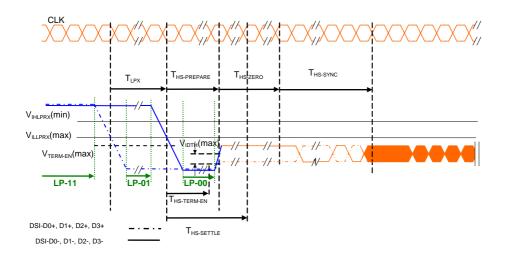

2.4.5.2.1 HSDT Start of Transmission

The display module DSI D0+/-, D1+/-, D2+/- and D3+/- enter High Speed High Transmission as follows:-

| Step | Host                                            | Display module                                     |

|------|-------------------------------------------------|----------------------------------------------------|

| 1    | Drives Stop State LP-11                         | Monitors the Stop State                            |

| 2    | Drives HS-Request state LP-01 for time TLPX.    | Monitors the transition from LP-11 to LP-01        |

| 3    | Drives LP-00 for time T <sub>HS-PREPARE</sub> . | Monitors the transition from LP-01 to LP-00        |

|      |                                                 | and enables the Termination Impedance              |

|      |                                                 | after time T <sub>HS-TERM-EN</sub> .               |

| 4    | Drives HS-0 for a time T <sub>HS-ZERO</sub> .   | Enables HS-RX and timeout T <sub>HS-SETTLE</sub> . |

| 5    |                                                 | Monitoring for Leader-Sequence "011101"            |

| 6    | Inserts the HS Sync-Sequence "00011101"         |                                                    |

|      | beginning on a clock rising edge.               |                                                    |

| 7    |                                                 | Synchronises after recognising                     |

|      |                                                 | Leader-Sequence "011101".                          |

| 8    | Transmit High Speed Data                        | Receive High Speed data.                           |

The sequence for starting High Speed Data Transmission on the DSI bus is shown in the following figure:-

Figure 3 – HSDT Start Sequence.

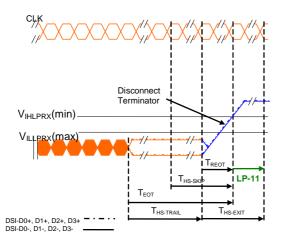

2.4.5.2.2 HSDT End of Transmission

The display module DSI D0+/-, D1+/-, D2+/- and D3+/- exits High Speed High Transmission as follows:-

| Step | Host                                                                                                                                                                           | Display module                                                                                                                   |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 1    | End High Speed Data Transmission                                                                                                                                               | Receive the last data                                                                                                            |

| 2    | Host drives HS-1 for time $T_{HS-TRAIL}$ if the last data<br>bit transmitted was HS-0<br>Host drives HS-0 for time $T_{HS-TRAIL}$ if the last data<br>bit transmitted was HS-1 |                                                                                                                                  |

| 3    | Host Drives stop-state LP-11 for a minimum time $T_{\text{HS-EXIT}}$ .                                                                                                         | Monitors the entering stop state LP-11, disables the Termination Impedance and ignores the bits sent during time $T_{HS-SKIP}$ . |

The sequence for ending High Speed Data Transmission on the DSI bus is shown in the following figure:-

Figure 4 – HSDT End Sequence.

Japan Display Inc.

#### 2.4.5.3 Escape Mode

Escape Mode applies only to Data Lane D0+/-. This is a special mode of operation in the Low Power state and is valid in both the forward (Host to Display) and Reverse directions (Display to Host).

The Display module supports the following escape modes:-

| Escape Mode Action          | Command Type | Entry Command Pattern                         | Note |

|-----------------------------|--------------|-----------------------------------------------|------|

|                             | Mode/Trigger | (1 <sup>st</sup> bit to last bit transmitted) |      |

| Low Power Data Transmission | Mode         | 1110 0001 bin                                 |      |

| Ultra Low Power State       | Mode         | 0001 1110 bin                                 |      |

| Remote Application          | Trigger      | 0110 0010 bin                                 |      |

| Acknowledge                 | Trigger      | 0010 0001 bin                                 |      |

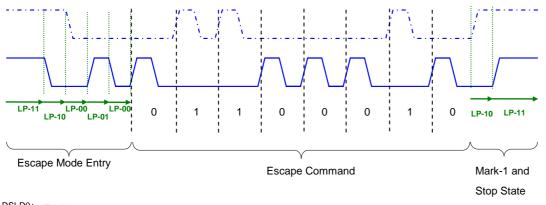

It is only possible to enter Escape Mode from Control Mode by the sequence

$LP\text{-}11 \rightarrow LP\text{-}10 \rightarrow LP\text{-}00 \rightarrow LP\text{-}01 \rightarrow LP\text{-}00.$

If LP-11 state is detected before the final bridge state LP-00, then the Escape Mode entry procedure will be aborted and the Display Module will return to the stop state (LP-11).

To exit Escape mode the end sequence LP-10  $\rightarrow$  LP-00 is applied.

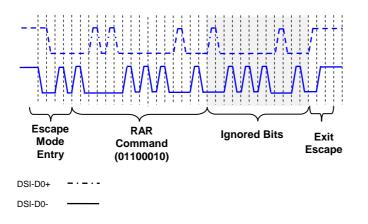

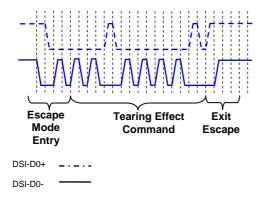

The following example shows the Escape Mode Entry and exit along with Reset-Trigger Escape Command.

DSI-D0+ -·-·-DSI-D0- \_\_\_\_

Figure 5 – Escape Mode Sequence.

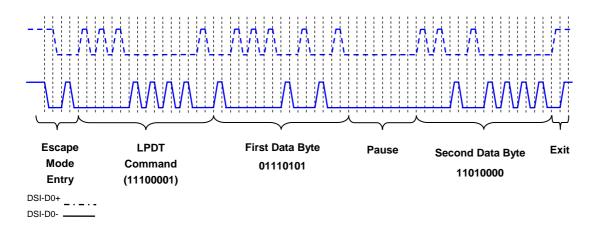

#### 2.4.5.3.1 Low Power Data Transmission.

Data can be written from the Host to the Display in Low Power Data Transmission. Firstly the Escape Mode Entry Procedure is sent followed by the (LPDT) Escape Command 11100001. Data is encoded by the same Spaced One-Hot code used for Entry Commands and it is possible to add a pause between data bytes by holding both DSI D0+/- lines low as shown in the following example.

The DSI D0+/-, DSI D1+/-, DSI D2+/- and D3+/- data lanes can enter Ultra Low Power State, in this condition both data lines are kept Low by

the Host (LP-00).

To enter Ultra Low Power State, the Escape Command 00011110 is sent after the Escape mode Entry Procedure. To exit Ultra Low Power State, the Mark01 state (LP-10) should be applied for minimum 1msec followed by the stop state (LP-11). The following diagram explains Ultra Low Power State entry and exit:-

Figure 7 – Ultra Low Power State Example.

#### 2.4.5.3.3 Remote Application Reset

The DSI D0+/-, DSI D1+/- and DSI D2+/- data lanes can enter Remote Application Reset State, in this condition any data bits sent on the data lanes are ignored before the Stop state is received as shown in following example:-

Figure 8 – Remote Application Reset Example.

| Product Number | ACX450AKN-7 | <b>Revision Number</b> | 04 | Page 18/66 |

|----------------|-------------|------------------------|----|------------|

|                |             |                        |    | -          |

#### 2.4.5.3.4 Acknowledge Trigger

The Acknowledge Trigger Escape command is used by the host to request an Acknowledge that the preceding command or data sent from the host was successfully received.

To request an Acknowledge, the host will send the Escape Command 00100001 after the Escape Entry Procedure as shown in the following diagram:-

Figure 9 – Acknowledge Trigger.

After sending the Acknowledge Request the host will normally send the Bus Turnaround Command and wait for the Display Module to send the Acknowledge response.

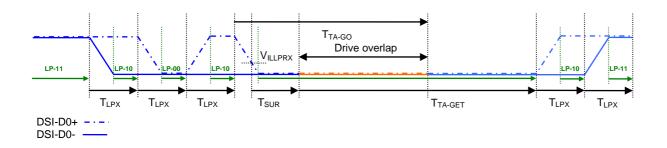

#### 2.4.5.4 Bus Turnaround

The Bus Turnaround procedure can be instigated by either the host or the Display module when they want to receive information from the other device. The same sequence is used regardless of whether the host or the display is performing the turnaround request. The sequence is as follows:-

| Step | Initial Tx side => Final Rx Side                                                            | Initial Rx side => Final Tx Side                      |

|------|---------------------------------------------------------------------------------------------|-------------------------------------------------------|

| 1    | Drives Stop State LP-11                                                                     | Monitors the Stop State                               |

| 2    | Drives LP-Request state LP-10 for time TLPX.                                                | Monitors the transition from LP-11 to LP-10           |

| 3    | Drives LP-00 for time T <sub>LPX</sub> .                                                    | Monitors the transition from LP-10 to LP-00.          |

| 4    | Drives LP-10 for a time T <sub>LPX</sub> .                                                  | Monitors the transition from LP-00 to LP-10.          |

| 5    | Drives LP-00 for a time T <sub>TA-GO</sub> .                                                | Monitors the transition from LP-10 to LP-00 and waits |

|      |                                                                                             | for a time T <sub>TA-SURE</sub> .                     |

| 6    |                                                                                             | Drives LP-00 for a time T <sub>TA-GET</sub> .         |

| 7    | Stops driving the DSI Lanes and output drivers                                              |                                                       |

|      | become High-Z. Receiver is monitoring for LP-10                                             |                                                       |

|      | state.                                                                                      |                                                       |

| 8    |                                                                                             | Drives LP-10 for a time T <sub>LPX</sub> .            |

| 9    | Monitors LP-10 and interprets this as an                                                    |                                                       |

|      | acknowledgement that the other side has taken over the bus. Waits for Stop state (LP-11) to |                                                       |

|      | complete the procedure                                                                      |                                                       |

| 10   |                                                                                             | Drives LP-11 for a time TLPX.                         |

| 11   | Monitors the transition from LP-10 to LP-11 and                                             |                                                       |

|      | interprets this as Turnaround complete. Switched                                            |                                                       |

|      | to LP Rx mode and waits for next action from the                                            |                                                       |

|      | other side.                                                                                 |                                                       |

The Bus Turnaround Sequence is as follows:-

#### Figure 10 – Bus Turnaround Sequence.

The bus turnaround procedure can be aborted if a Stop state (LP-11) is sent before the bus starts to be driven LP-00 at the beginning of time period  $T_{SURE}$  in Fig10. In this event, the lanes will return to the stop state LP-11. It is not possible to abort the turnaround procedure after LP-00 at the time  $T_{SURE}$  has started to be driven.

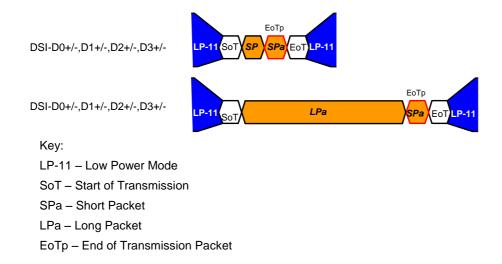

## 2.4.6 Packet Level Communication

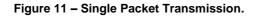

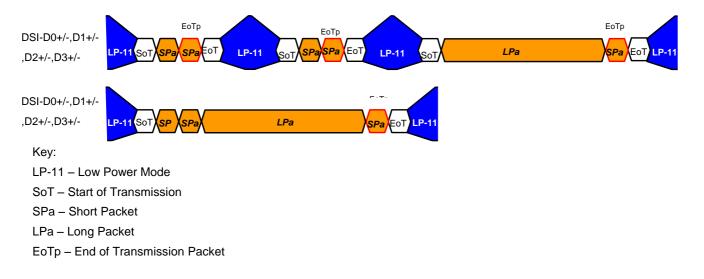

Data is transferred between host and the display module and vice-versa by means of packet Level communication. Packet communication applies to both Low Power Data Transmission mode (LPDT) and High Speed Data Transmission (HSDT). A Transmission may consist of both Short Packets (SPa) and Long Packets (LPa), it may contain only one packet or multiple packets. Also multiple packets may consist of both Short (SPa) and Long (LPa) packets.

For High Speed Mode, Each Transmission requires Start of Transmission SoT, End of Transmission Packet (which is the last transmitted packet (SPa)) and End of Transmission (EoT).

Example of single Short Packet Transmission and single Long Packet Transmission.

Example of the same multiple Short and Long Packet Transmissions sent in Separate and Single transmissions.

Japan Display Inc.

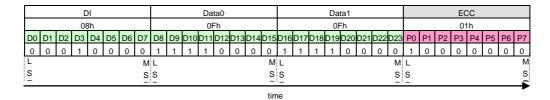

## 2.4.6.1 Data Byte Order in HSDT

When 3 channels are in use, data is always transmitted in the order of the First Byte appears on DSI Lane 0, the second byte on DSI data Lane 1, third on Data Lane 2, fourth on DSI data lane 0 and so on.

Both DSI-D0+/-, DSI-D1+/-, DSI-D2+/- and DSI-D3+/- will always start data transmission simultaneously with SoT however depending upon the number of bytes being transferred one lane may complete transfer before the other lane.

#### 2.4.6.2 Packet Bit and Byte Order

For each byte in a packet, the bit order is the LSB is sent first and the MSB is sent last. For packets with multiple bytes, the least significant byte is sent first and the most significant byte is sent last.

| Product Number ACX450AKN-7 | Revision Number 04 | Page 22/66 |

|----------------------------|--------------------|------------|

|----------------------------|--------------------|------------|

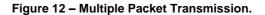

#### 2.4.6.3 Short Packet Format

Short packets are 4 bytes in length. They are used mainly for sending commands with either none or one parameter. The structure of the packet is as follows, this example is using High Speed Data Transfer, Low Power Data Transfer can also be used.:-

Packet header

Figure 13 – Short Packet Format.

Where:-

DI = Data Identifier Byte

Contains the Virtual Channel Identifier and the Data Type information.

Data0 = LSB Byte

Data1 = MSB Byte

ECC = Error Correction Code

8-Bit Error Code Correction for the correction of single-bit error and the detection of 2-bit errors.

Bit order on the short packet appears as shown in the following example:-

| DI       | Data0           | Data1    | ECC             |  |  |

|----------|-----------------|----------|-----------------|--|--|

| 15h      | 35h             | 01h      | 1Eh             |  |  |

| 10101000 | 1 0 1 0 1 1 0 0 | 10000000 | 0 1 1 1 1 0 0 0 |  |  |

| L M      | L M             | L M      | L M             |  |  |

Figure 14 – Short Packet Example.

| Product Number ACX450AKN-7 | Revision Number 04 | Page 23/66 |

|----------------------------|--------------------|------------|

|----------------------------|--------------------|------------|

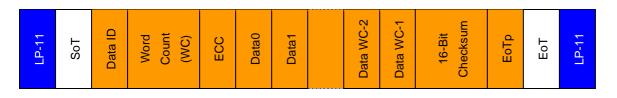

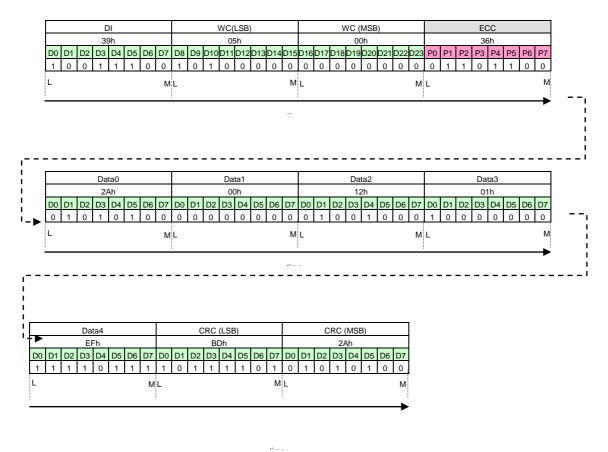

#### 2.4.6.4 Long Packet Format

Long packets are minimum 6bytes in length and can contain up to a maximum of 65,536 data bytes. The structure of the packet is as follows, this example is using High Speed Data Transfer, Low Power Data Transfer can also be used:-

Where:-

Data ID = Data Identifier Byte

Contains the Virtual Channel Identifier and the Data Type information.

#### WC = 16-Bit Word Count

The word count informs how many data bytes will be sent in the packet payload from this the Display Module can determine the packet end.

#### ECC = Error Correction Code

8-Bit Error Code Correction for the correction of single-bit error and the detection of 2-bit errors within the Packet Header.

## Data0→Data WC-1 = Packet Data (Payload)

16-Bit Checksum = Checksum for the transmitted packet data payload.

The Display module will calculate the Checksum value from the received data and compare with the transmitted Checksum value from the host. The display module will report an error at the next Bus Turnaround if the values are not equal.

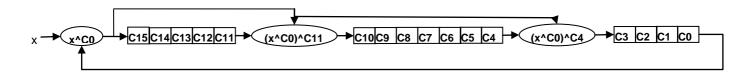

Bit order on the long packet appears as shown in the following example:-

| DI     | WC(LS Byte)   | WC(MS Byte)     | ECC               | Data     | CRC(LS Byte)    | CRC(MS Byte)    |

|--------|---------------|-----------------|-------------------|----------|-----------------|-----------------|

| 29h    | 01h           | 00h             | 06h               | 01h      | 0Eh             | 1Eh             |

| 100101 | 0 1 0 0 0 0 0 | 0 0 0 0 0 0 0 0 | 0 0 1 1 0 0 0 0 0 | 10000000 | 0 1 1 1 0 0 0 0 | 0 1 1 1 1 0 0 0 |

|        |               |                 |                   |          |                 |                 |

| L      | ML            | ML              | ML N              | IL N     | L M             | L M             |

|        |               |                 |                   |          |                 |                 |

Figure 16 – Long Packet Example.

#### 2.4.6.5 Data Identifier Byte

The Data Identifier Byte serves 2 purposes. One is the Virtual Channel Identification and the other specifies the Data type:-

| Bit7       | Bit6       | Bit5 | Bit4 | Bit3    | Bit2     | Bit1 | Bit0 |

|------------|------------|------|------|---------|----------|------|------|

| Virtual Ch | annel (VC) |      |      | Data Ty | rpe (DT) |      |      |

2.4.6.5.1 Virtual Channel Identifier (VC)

The Virtual Channel can allow addressing up to 4 channels, in other words 4 different devices connected to the same receiver. This display module uses virtual channel 0, i.e. Bits 7 and  $6 = 00^{\circ}$ .

When the display module sends information back to the host it will also assign Virtual Channel 0 in its packet header.

2.4.6.5.2 Data Type Field (DT)

The Data Type Field informs if the packet is a Short (SPa) or Long Packet (LPa), it also contains information about the type of data transaction from the host to the display module and also from the display module to the host. The supported data transaction types are listed in the following tables:-

Data Types from the Host to the Display Module.

| Data Type |      | Dat  | a type | e (bin | ary) |      |                                              | Packet |      |

|-----------|------|------|--------|--------|------|------|----------------------------------------------|--------|------|

| (Hex]     | Bit5 | Bit4 | Bit3   | Bit2   | Bit1 | Bit0 | Description                                  | Size   | Note |

| 01h       | 0    | 0    | 0      | 0      | 0    | 1    | Sync Event, V Sync Start                     | Short  |      |

| 21h       | 1    | 0    | 0      | 0      | 0    | 1    | Sync Event, H Sync Start                     | Short  |      |

| 08h       | 0    | 0    | 1      | 0      | 0    | 0    | End of Transmission Packet (Note 1).         | Short  |      |

| 22h       | 0    | 1    | 0      | 0      | 1    | 0    | Shut Down Peripheral command                 | Short  |      |

| 32h       | 1    | 1    | 0      | 0      | 1    | 0    | Turn On Peripheral Command                   | Short  |      |

| 13h       | 0    | 1    | 0      | 0      | 1    | 1    | Generic Short WRITE 1 parameter              | Short  | 1, 2 |

| 23h       | 1    | 0    | 0      | 0      | 1    | 1    | Generic Short WRITE, 2 parameters            | Short  | 1, 3 |

| 29h       | 1    | 0    | 1      | 0      | 0    | 1    | Generic Long Write                           | Long   | 1    |

| 14h       | 0    | 1    | 0      | 1      | 0    | 0    | Generic Short READ, 1 parameter              | Short  | 1, 2 |

| 24h       | 1    | 0    | 0      | 1      | 0    | 0    | Generic Short READ, 2 parameters             | Short  | 1, 3 |

| 05h       | 0    | 0    | 0      | 1      | 0    | 1    | DCS WRITE with No Parameter.                 | Short  |      |

| 15h       | 0    | 1    | 0      | 1      | 0    | 1    | DCS WRITE with One Parameter.                | Short  |      |

| 06h       | 0    | 0    | 0      | 1      | 1    | 0    | DCS READ with No Parameter.                  | Short  |      |

| 37h       | 1    | 1    | 0      | 1      | 1    | 1    | Set Maximum Return Packet Size               | Short  |      |

| 09h       | 0    | 0    | 1      | 0      | 0    | 1    | Null Packet, No data (Note 2).               | Long   |      |

| 19h       | 0    | 1    | 1      | 0      | 0    | 1    | Blanking Packet, no data                     | Long   |      |

| 39h       | 1    | 1    | 1      | 0      | 0    | 1    | DCS WRITE Long                               | Long   |      |

| 2Eh       | 1    | 0    | 1      | 1      | 1    | 0    | Loosely Packed Pixel Stream, 18bit RGB 6-6-6 | Long   |      |

|           |      |      |        |        |      |      | Format                                       |        |      |

| 3Eh       | 1    | 1    | 1      | 1      | 1    | 0    | Packed Pixel Stream,24bit RGB 8-8-8 Format   | Long   |      |

| other     | х    | х    | х      | х      | х    | х    | DO NOT USE                                   |        |      |

|           |      |      |        |        |      |      | All unspecified codes are reserved           |        |      |

Notes:

1. The receiver process packets with data type (Generic Write/Read) the same way as data type (DCS Write / Read).

2. Generic Write/Read with 1 parameter: Payload Bytes = Command + 00h.

3. Generic Write/Read with 2 parameter: Payload Bytes = Command + Parameter.

4. The receiver will ignore packets with data type that neither listed in table above nor in MIPI DSI spec.

#### Japan Display Inc.

Data Types from the Display Module to the Host.

| Data Type |      | Data | а Тур | e (Bir | nary) |      | Description                                 | Packet | Sumbol   |

|-----------|------|------|-------|--------|-------|------|---------------------------------------------|--------|----------|

| (Hex)     | Bit5 | Bit4 | Bit3  | Bit2   | Bit1  | Bit0 | Description                                 | Size   | Symbol   |

| 02h       | 0    | 0    | 0     | 0      | 1     | 0    | Acknowledge with Error Report.              | Short  | AwER     |

| 1Ch       | 0    | 1    | 1     | 1      | 0     | 0    | DCS READ Long Response.                     | Long   | DCSRR-L  |

| 21h       | 1    | 0    | 0     | 0      | 0     | 1    | DCS READ Short Response, 1 Byte Returned.   | Short  | DCSRR1-S |

| 22h       | 1    | 0    | 0     | 0      | 1     | 0    | DCS READ Short Response, 2 Bytes Returned.  | Short  | DSCRR2-S |

| 1Ah       | 0    | 1    | 1     | 0      | 1     | 0    | Generic Read Long Response                  | Long   | GENRR-L  |

| 11h       | 0    | 1    | 0     | 0      | 0     | 1    | Generic Read Short Response, 1byte returned | Short  | GENRR1-S |

| 12h       | 0    | 1    | 0     | 0      | 1     | 0    | Generic Read Short Response, 2byte returned | Short  | GENRR2-S |

Notes:

The receiver will ignore other Data Type (DT) if they are not defined on tables: "Data Type (DT) from the MCU to the Display Module (or Other Devices)" or "Data Type (DT) from the Display Module (or Other Devices) to the MCU".

#### 2.4.6.6 Packet Data on the Short Packet (SPa)

Packet data is 2 bytes long in a short packet. If the length of data to be sent requires only 1 byte, then the data in the 2<sup>nd</sup> byte (Data 1) will be set as all zero.

Packet data is always sent in the order Data0 first, followed by Data1as shown in the below example:-

| 15h 35h 01h | Eh   |

|-------------|------|

|             |      |

|             | 1000 |

|             |      |

| L ML ML ML  | M    |

## Figure 17 – Data on the Short Packet.

## 2.4.6.7 Word Count (WC) on the Long Packet.

The word count is used to indicate how many bytes of data will be sent after the Packet header.

The word count is 2 bytes long and can define a minimum of 0 bytes to a maximum of 65,536 bytes to be sent.

The sending order of the 2 word count bytes is the Least Significant Byte is always sent first followed by the most Significant Byte.

| DI     | WC (L  | S Byte) | WC (MS Byte)  | ECC             |

|--------|--------|---------|---------------|-----------------|

| 29h    | C      | )1h     | 00h           | 06h             |

| 100101 | 001000 | 00000   | 0 0 0 0 0 0 0 | 0 1 1 0 0 0 0 0 |

| L      | ML     | ML      | L M           | L M             |

## Figure 18 – Word Count on the Long Packet.

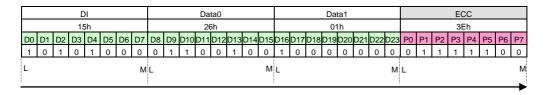

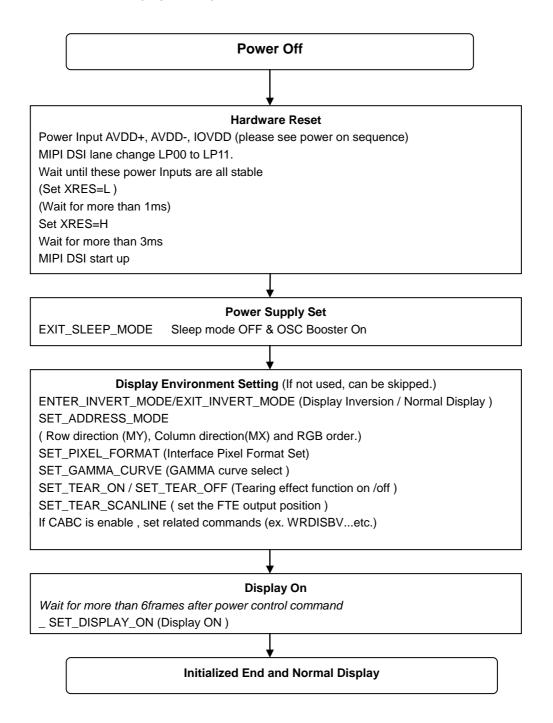

## 2.4.6.8 Error Correction Code (ECC)

The Error Correction Code allows single-bit errors to be corrected and 2 or more-bit errors to be detected in the Packet Header. It is used for both Short (Spa) and Long (Lpa) packets.

When receiving data transmission from the host, the display module will generate ECC byte from the received packet header Data Identifier (DI) and Data0, Data1 bytes in the case of SPa and Data Identifier (DI), WC (LS Byte), WC (MS Byte) in the case of LPa. It will compare this generated ECC byte with that sent on the Packet Header to determine if error has occurred or not.

When sending Data Transmission to the host, the Display Module will generate the ECC byte from the packet data to be sent and appends to the packet header. The ECC byte is always the last transmitted byte on the packet header as highlighted in this example for the Short Packet (SPa):-

## Figure 19 – Error Correction Code on the Short Packet.

The Pink coloured bits are the error correction bits.

The Green coloured bits are the bits that can be corrected by the ECC.

The device transmitting the data sends data D[23..0] and ECC P[7..0]. An 8-bit ECC allows correction for up to 64bits, however in this application only 24bits require to be checked for correction, so bits P7 and P6 are always set to '00' on the ECC. The remaining bits are generated as follows:-

P7=0 P6=0 P5=D10^D11^D12^D13^D14^D15^D16^D17^D18^D19^D21^D22^D23 P4=D4^D5^D6^D7^D8^D9^D16^D17^D18^D19^D20^D22^D23 P3=D1^D2^D3^D7^D8^D9^D13^D14^D15^D19^D20^D21^D23 P2=D0^D2^D3^D5^D6^D9^D11^D12^D15^D18^D20^D21^D22 P1=D0^D1^D3^D4^D6^D8^D10^D12^D14^D17^D20^D21^D22^D23 P0=D0^D1^D2^D4^D5^D7^D10^D11^D13^D16^D20^D21^D22^D23

where " $^{"}$  = XOR function.

The receiving device generates the ECC from the received data D[23..0] by the same function as above to generate IECC (internal ECC). The function ECC^IECC is performed and the result OP[7..0] determines if error has occurred or not.

- If the result of ECC^IECC = 00h, then there is no error in the data received.

- If the result of ECC^IECC ≠ 00h and is listed on the table in Fig20, then the error is a single bit error and that corresponding bit can be corrected. Also the "ECC error, single bit (detected and corrected)" bit is flagged.

- If the result of ECC^IECC ≠ 00h and is not listed on the table in Fig20, then the error is in 2bits or more and cannot be corrected, the packet is ignored and the "ECC error, multi-bit (detected, not corrected)" bit is flagged.

| Data Bit | OP7 | OP6 | OP5 | OP4 | OP3 | OP2 | OP1 | OP0 | ECC^IECC |

|----------|-----|-----|-----|-----|-----|-----|-----|-----|----------|

| D0       | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 1   | 07h      |

| D1       | 0   | 0   | 0   | 0   | 1   | 0   | 1   | 1   | 0Bh      |

| D2       | 0   | 0   | 0   | 0   | 1   | 1   | 0   | 1   | 0Dh      |

| D3       | 0   | 0   | 0   | 0   | 1   | 1   | 1   | 0   | 0Eh      |

| D4       | 0   | 0   | 0   | 1   | 0   | 0   | 1   | 1   | 13h      |

| D5       | 0   | 0   | 0   | 1   | 0   | 1   | 0   | 1   | 15h      |

| D6       | 0   | 0   | 0   | 1   | 0   | 1   | 1   | 0   | 16h      |

| D7       | 0   | 0   | 0   | 1   | 1   | 0   | 0   | 1   | 19h      |

| D8       | 0   | 0   | 0   | 1   | 1   | 0   | 1   | 0   | 1Ah      |

| D9       | 0   | 0   | 0   | 1   | 1   | 1   | 0   | 0   | 1Ch      |

| D10      | 0   | 0   | 1   | 0   | 0   | 0   | 1   | 1   | 23h      |

| D11      | 0   | 0   | 1   | 0   | 0   | 1   | 0   | 1   | 25h      |

| D12      | 0   | 0   | 1   | 0   | 0   | 1   | 1   | 0   | 26h      |

| D13      | 0   | 0   | 1   | 0   | 1   | 0   | 0   | 1   | 29h      |

| D14      | 0   | 0   | 1   | 0   | 1   | 0   | 1   | 0   | 2Ah      |

| D15      | 0   | 0   | 1   | 0   | 1   | 1   | 0   | 0   | 2Ch      |

| D16      | 0   | 0   | 1   | 1   | 0   | 0   | 0   | 1   | 31h      |

| D17      | 0   | 0   | 1   | 1   | 0   | 0   | 1   | 0   | 32h      |

| D18      | 0   | 0   | 1   | 1   | 0   | 1   | 0   | 0   | 34h      |

| D19      | 0   | 0   | 1   | 1   | 1   | 0   | 0   | 0   | 38h      |

| D20      | 0   | 0   | 0   | 1   | 1   | 1   | 1   | 1   | 1Fh      |

| D21      | 0   | 0   | 1   | 0   | 1   | 1   | 1   | 1   | 2Fh      |

| D22      | 0   | 0   | 1   | 1   | 0   | 1   | 1   | 1   | 37h      |

| D23      | 0   | 0   | 1   | 1   | 1   | 0   | 1   | 1   | 3Bh      |

## Figure 20 – Table of One Bit Error Value for ECC

For example if the value of the function ECC/IECC (OP[7..0]) = 1Fh, then by referring to the above table, this means there has been a one bit error on bit D20. The receiver can correct this error by complementing the bit value of D20 and storing the modified value.

#### 2.4.6.9 Packet Footer on Long Packet (LPa)

To detect errors in transmission of Long Packets, a checksum is calculated over the payload portion of the data packet. Long packets can transmit from 0 to 65,536 bytes, on the special case where there are 0 bytes transmitted, the Checksum value will be fixed to FFFFh.

The checksum can only detect the presence of one or more errors on a transmitted data payload, it cannot make any correction.

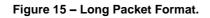

The checksum is realised by a 16-bit Cyclic Redundancy Check calculation by the polynomial x^16+x^12+x^5+x^0

Figure 21 – 16-Bit Cyclic Redundancy Check Calculation

In the transmitting device, before Packet Data transmission starts, the CRC shift register is initialized to FFFFh, then packet data (excluding the Packet Header) enters as a bitwise stream at "x" in above figure from the Least Significant Bit first.

After all the Bytes in the packet payload have passed through the CRC shift register, then the shift register contains the Checksum Value C[15..0]. This is appended to the data stream and passed to the receiver.

The receiver will calculate Checksum by the same method and compare its calculated value versus the transmitted value. If an error is detected, then the "Checksum Error" bit is flagged.

## 2.4.7 Host to Display Module Packet Transmissions.

#### 2.4.7.1 Display Command Set (DCS)

The Display Command Set is described in Section 0, it is used for sending commands from the Host to the Display Module. The Command is always set on Data0 and parameters are set on the following bytes.

In the case of Short Packet Transfer (SPa), if the command has no parameter, then the second byte (Data1) is set to 00h. If the command requires more than one parameter, then the Long Packet Transfer (LPa) is used.

The following transfer types are supported; please refer to the table in Section 2.4.6.5.2 for the various Data Field Type Code

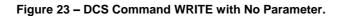

#### 2.4.7.2 DCS Command WRITE with No Parameter, (DT=05h).

DCS Command WRITE with No Parameter is used for writing a command which has no parameter to the Display Module, always using Short Packet (SPa). The following commands can be sent by this method:-

Example of sending Sleep In (10h) command:-

|    |    |    | D  | DI |    |    |    |    |    |     | Da  | ta0 |     |     |     |     |     |     | Da  | ta1 |     |     |     |    |    |    | EC | CC |    |    |    |

|----|----|----|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|

|    |    |    | 05 | 5h |    |    |    |    |    |     | 10  | Dh  |     |     |     |     |     |     | 0   | Dh  |     |     |     |    |    |    | 20 | Ch |    |    |    |

| D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8 | D9 | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | P0 | P1 | P2 | P3 | P4 | P5 | P6 | P7 |

| 1  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 1  | 1  | 0  | 1  | 0  | 0  |

| L  |    |    |    |    |    |    | М  | L  |    |     |     |     |     |     | М   | L   |     |     |     |     |     |     | М   | L  |    |    |    |    |    |    | М  |

#### Figure 22 – DCS Command WRITE with No Parameter.

#### 2.4.7.3 DCS Command Write with 1 Parameter, (DT=15h).

DCS Command WRITE with 1 Parameter is used for writing a command which has 1 parameter to the Display Module, always using Short Packet (SPa).

Example of sending Gamma Set (26h) command:-

Japan Display Inc.

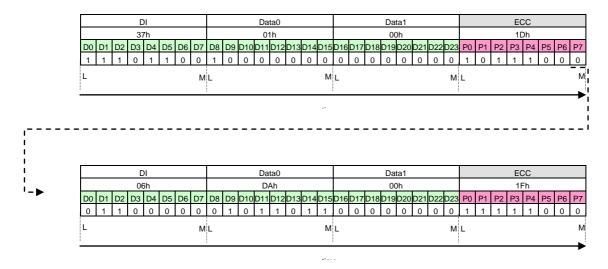

## 2.4.7.4 DCS Command Read with No Parameter, (DT=06h) & Set Maximum Return Size (DT=37h).

DCS Command Read with no Parameter is used to request data from the Display Module, always using Short Packet (SPa). Before sending this Data Type, the host has to define to the Display Module what is the maximum size of the return packet. This is defined by Data Type Set Maximum Return Size (DT=37h). Following this read request, the Bus Turnaround shall be performed so the Display Module can send back the requested data. The following read commands can be requested by this method:-

Example of requesting Read ID1 (DAh) command:-

Firstly send the maximum return size (DT=37h) then Read Command with no parameter (DT=06h).

Figure 24 – DCS Command Read.

After sending the Bus Turnaround Command, the Display Module will reply with either of the following:-

- 1. An acknowledge with Error Report (AwER) in a short packet if there is an error to report. See Section 2.4.9.1

- 2. Read data for the requested read command in Short (SPa) or Long (LPa) packets.

## Note:

The Default value of the Maximum Return Size (DT=37h) after Power On, Hardware or Software Reset is 1.

## 2.4.7.5 Null Packet, No data, (DT=09h)

The purpose of this command is to keep the Data Lanes in High Speed Mode if required. The format of this packet is Long Packet (LPa). Any data included in a Null Packet is completely ignored by the Display Module.

Example of Sending a Null Packet of 5 bytes in length:-

Figure 25 – Null Packet, No Data.

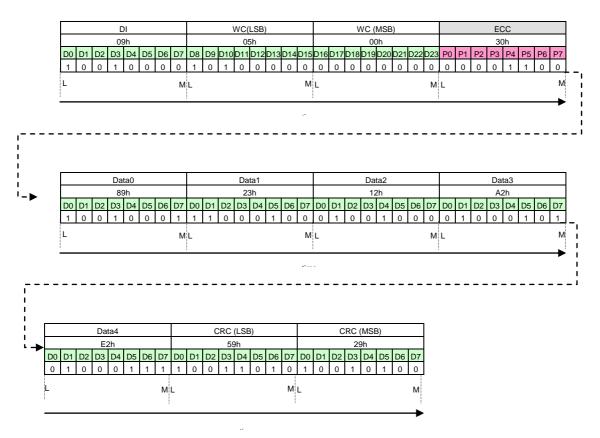

#### 2.4.7.6 DCS WRITE Long (DT=39h).

DCS WRITE Long is used for writing commands both with and without parameter types to the Display Module, always using Long Packet (LPa). The following commands can be sent by this method:-

Example 1 - Sending Sleep In (10h) command (DCS Command with no Parameter):-

Figure 26 – Long Packet Example 1.

Example 2 - Sending Gamma Set (26h) command (DCS Command with one Parameter):-

| DI                      | WC(LSB)                          | WC (MSB)                 | ECC                       |

|-------------------------|----------------------------------|--------------------------|---------------------------|

| 39h                     | 02h                              | 00h                      | 13h                       |

| D0 D1 D2 D3 D4 D5 D6 D7 | 7 D8 D9 D10 D11 D12 D13 D14 D15  | D16D17D18D19D20D21D22D23 | 3 P0 P1 P2 P3 P4 P5 P6 P7 |

| 1 0 0 1 1 1 0 0         | 0 1 0 0 0 0 0 0                  | 0 0 0 0 0 0 0 0          | 1 1 0 0 1 0 0 0           |

| - 1                     | ۸L M                             | L M                      | L N                       |

|                         |                                  |                          |                           |

|                         |                                  |                          |                           |

| Data0                   | Data1                            | CRC (LSB)                | CRC (MSB)                 |

| Data0<br>26h            | Data1<br>01h                     | CRC (LSB)<br>D2h         | CRC (MSB)<br>96h          |

| 26h                     |                                  | D2h                      | 96h                       |

| 26h                     | 01h<br>7 D0 D1 D2 D3 D4 D5 D6 D7 | D2h                      | 96h                       |

Figure 27 – Long Packet Example 2.

Example 3 - Sending Column Address Set (2Ah) command (DCS Command with four Parameters):-

Figure 28 – Long Packet Example 3.

### 2.4.7.7 End of Transmission Packet (DT=08h)

The purpose of the End of Transmission Packet (EoTp) is to indicate to the Display module that the host intends to terminate High Speed Data Transmission. It is always using Short Packet (SPa). This packet is always added after the last payload data and before the End of Transmission Sequence.

It is possible that the EoTp is sent in Low Power Mode, in such case there is no influence to the display module.

Example of End of Transmission Packet:-

Figure 29 – End of Transmission Packet.

### 2.4.7.8 Generic Short WRITE Packet with 1, or 2 parameters (DT=13h or 23h)

Generic Short WRITE command is a Short packet type for sending generic command and data to the LCD.

The complete packet shall be four bytes in length including an ECC byte. The two Data Type MSBs, bits [5:4], indicate the number of valid parameters (1, or 2). For single-byte parameters, the parameter shall be sent in the first data byte following the DI byte and the second data byte shall be set to 0x00.

### 2.4.7.9 Generic Short Read Packet with 1, or 2 parameters (DT=14h or 24h)

Generic READ request is a Short packet requesting data from the LCD.

Returned data may be of Short or Long packet format. Note the Set Max Return Packet Size command limits the size of returning packets so that the host processor can prevent buffer overflow conditions when receiving data from the peripheral. If the returning block of data is larger than the maximum return packet size specified, the read response will require more than one transmission. The host processor shall send multiple Generic READ requests in separate transmissions if the requested data block is larger than the maximum packet size.

### 2.4.7.10 Generic Long Write (DT=29h)

Generic Long Write Packet is used to transmit arbitrary blocks of data from a host processor to a peripheral in a Long packet. The packet consists of the DI byte, a two-byte WC, an ECC byte, a payload of length WC bytes and a two-byte checksum as DCS Long Write.

### 2.4.8 Host to Display Module Packet Transmissions for Video mode operation

### 2.4.8.1 Sync Event (V Start, H Start) (DT=01h, 21h)

Sync Events are Short packets to represent timing information as accurately as possible a V sync and H Sync Start event. Timing position relative to active pixel data, e.g. front and back porch display timing, may be accurately conveyed to the LCD. See section for timing details of interlaced video formats. Sync events may be concatenated with blanking packets to transport inter-line timing accurately and avoid the overhead of switching between LPS and HS for every event. Note there is a power penalty for keeping the data line in HS mode, however.

#### 2.4.8.2 Blanking Packet (Long) (DT=19h)

A Blanking packet is used to convey blanking timing information in a Long packet. Normally, the packet represents a period between active scan lines of a Video Mode display, where traditional display timing is provided from the host processor to the display module. The blanking period may have Sync Event packets interspersed between blanking segments. Like all packets, the Blanking packet contents shall be an integer number of bytes. Blanking packets may contain arbitrary data as payload.

### 2.4.8.3 Loosely Packed Pixel Stream (Long) (DT=2Eh)

In the 18-bit Pixel Loosely Packed format, each R, G, or B color component is six bits, but is shifted to the upper bits of the byte, such that the valid pixel bits occupy bits [7:2] of each byte as shown in Figure 27. Bits [1:0] of each payload byte representing active pixels are ignored. As a result, each pixel requires three bytes as it is transmitted across the Link. This requires more bandwidth than the "packed" format, but requires less shifting and multiplexing logic in the packing and unpacking functions on each end of the Link.

Figure 30 – 18-bit per Pixel (Loosely Packed) – RGB Color Format, Long Packet

## 2.4.8.4 Packed Pixel Stream , 24bit RGB 8-8-8 Format (Long) (DT=3Eh)

Packed Pixel Stream 24-Bit Format shown in Figure 28 is a Long packet. It is used to transmit image data formatted as 24-bit pixels to a Video Mode display module. The packet consists of the DI byte, a two-byte WC, an ECC byte, a payload of length WC bytes and a two-byte Checksum. The pixel format is red (8 bits), green (8 bits) and blue (8 bits), in that order. Each color component occupies one byte in the pixel stream; no components are split across byte boundaries. Within a color component, the LSB is sent first, the MSB last.

Figure 30– 24-bit per Pixel – RGB Color Format, Long Packet

### 2.4.8.5 Shutdown Peripheral Command (DT=22h)

Shutdown Peripheral command is a Short packet command that turns off the display in a Video Mode display module for power saving. Note the interface shall remain powered in order to receive the turn-on, or wake-up, command.

### 2.4.8.6 Turn On Peripheral Command (DT=32h)

Turn On Peripheral command is Short packet command that turns on the display in a Video Mode display module for normal display operation.

## 2.4.9 Display Module to Host Packet LP Transmissions.

### 2.4.9.1 Acknowledge and Error Report (DT=02h)

The purpose of the Acknowledge and Error Report is to feedback to the Host if any errors occurred in data transmissions from the Host to the Display Module since the previous communication from the Display Module to the Host. It is always using Short Packet (SPa).

Example of Acknowledge and Error Report:-

|    | DI Data0                                  |    |    |    |     |    |    |    |    |     | Da  | ta1 |     |     |     |     |     |     | EC  | CC  |     |     |     |    |    |    |    |    |    |    |    |

|----|-------------------------------------------|----|----|----|-----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|

|    |                                           |    | 02 | 2h | 00h |    |    |    |    |     |     | 0′  | 1h  |     |     |     |     |     |     | 3/  | ٩h  |     |     |    |    |    |    |    |    |    |    |

| D0 | D1                                        | D2 | D3 | D4 | D5  | D6 | D7 | D8 | D9 | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | P0 | P1 | P2 | P3 | P4 | P5 | P6 | P7 |

| 0  | 1                                         | 0  | 0  | 0  | 0   | 0  | 0  | 0  | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 1  | 0  | 1  | 1  | 1  | 0  | 0  |

| L  | D   1   0   0   0   0   0   0   0   0   0 |    |    |    |     |    |    |    | М  | L   |     |     |     |     |     |     | м   | L   |     |     |     |     |     |    | м  |    |    |    |    |    |    |

| :  |                                           |    |    |    |     |    |    |    |    |     |     |     |     |     |     |     |     |     |     |     |     |     |     |    |    |    |    |    |    |    | _  |

#### Figure 32 – End of Transmission Packet.

In general, after there has been communication from the Host to the Display Module followed by a Bus Turnaround BTA, the Display Module will respond with either an Acknowledge if there have been no recorded error or an "Acknowledge and Error Report" Packet if there are errors to report.

The following table provides a list of the bit assignments for the "Acknowledge and Error Report" packet:-

| Bit | Description                                    | Implementation |

|-----|------------------------------------------------|----------------|

| 0   | SoT Error                                      | No             |

| 1   | SoT Sync Error                                 | No             |

| 2   | EoT Sync Error                                 | No             |

| 3   | Escape Mode Entry Command Error                | Yes            |

| 4   | Low-Power Transmit Sync Error                  | Yes            |

| 5   | Any Protocol Timer Time-Out                    | No             |

| 6   | False Control Error                            | No             |

| 7   | Reserved                                       | -              |

| 8   | ECC Error, single-bit (detected and corrected) | Yes            |

| 9   | ECC Error, multi-bit (detected, not corrected) | Yes            |

| 10  | Checksum Error (Long Packet only)              | Yes            |

| 11  | DSI Data Type Not Recognized                   | Yes            |

| 12  | DSI Virtual Channel (VC) ID Invalid            | Yes            |

| 13  | Invalid Transmission Length                    | No             |

| 14  | Reserved                                       | -              |

| 15  | DSI Protocol Violation.                        | No             |

04

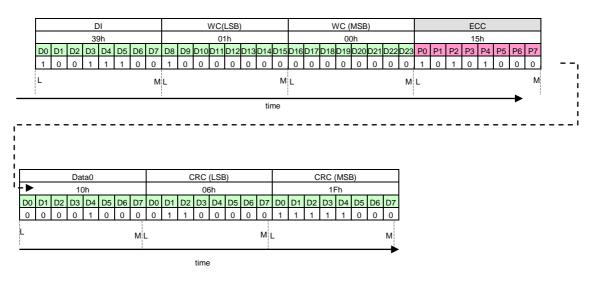

### 2.4.9.2 DCS Read Long Response (DT=1Ch)

DCS Read Long Response is used for sending requested read data from the Display Module back to the Host. The format is the same as Long Packet (LPa) writing from the Host to the Display Module i.e. It has a packet header containing the Data Identifier, two byte Word Count and an ECC byte.

Example - Sending 5 bytes of data:-

Figure 30 – DCS Read Long Response.

## 2.4.9.3 DCS Read Short Response, 1 Byte Returned (DT=21h)

DCS Read Short Response with 1 byte Returned is used for sending requested read data of 1 byte in length, always using Short Packet (SPa).

Example of sending DCS Read Short Response with 1 byte Returned:-

|   |     |    | DI Data0 |    |    |    |    |    |    |     |     | Da  | ta1 |      |     |     |     |     |     | EC  | cc  |     |     |     |    |    |    |    |    |    |    |    |

|---|-----|----|----------|----|----|----|----|----|----|-----|-----|-----|-----|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|

|   |     |    |          | 2  | 1h |    |    |    |    | 45h |     |     |     |      |     |     |     | 0   | Oh  |     |     |     |     |     |    | 0, | 1h |    |    |    |    |    |

| D | ) C | D1 | D2       | D3 | D4 | D5 | D6 | D7 | D8 | D9  | D10 | D11 | D12 | 2D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | P0 | P1 | P2 | P3 | P4 | P5 | P6 | P7 |

| 1 |     | 0  | 0        | 0  | 0  | 1  | 0  | 0  | 1  | 0   | 1   | 0   | 0   | 0    | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| L |     | ML |          |    |    |    |    |    | М  | L   |     |     |     |      |     |     | М   | L   |     |     |     |     |     |     | M  |    |    |    |    |    |    |    |

| Product Number | ACX450AKN-7 | Revision Number | 04 | Page 41/66 |

|----------------|-------------|-----------------|----|------------|

|                |             |                 |    | 0          |

## 2.4.9.4 DCS Read Short Response, 2 Byte Returned (DT=22h)

DCS Read Short Response with 2 bytes Returned is used for sending requested read data of 2 bytes in length, always using Short Packet (SPa).

Example of sending DCS Read Short Response with 2 bytes Returned:-

|    | DI Data0                        |    |    |    |    |    |    |    |     |     | Da  | ta1 |     |     |     |     |     |     | EC  | CC  |     |     |     |    |    |    |    |    |    |    |    |

|----|---------------------------------|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|

|    |                                 |    | 22 | 2h |    |    |    |    | 45h |     |     |     |     |     |     | 32  | 2h  |     |     |     |     |     |     | OF | -h |    |    |    |    |    |    |

| D0 | D1                              | D2 | D3 | D4 | D5 | D6 | D7 | D8 | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | P0 | P1 | P2 | P3 | P4 | P5 | P6 | P7 |

| 0  | 1                               | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 0   | 1   | 0   | 0   | 0   | 1   | 0   | 0   | 1   | 0   | 0   | 1   | 1   | 0   | 0   | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 0  |

| L  | 0 1 0 0 0 1 0 0 1 0 0 1 0 0 0 M |    |    |    |    |    |    | М  | L   |     |     |     |     |     |     | М   | L   |     |     |     |     |     |     | М  |    |    |    |    |    |    |    |

Figure 32 – DCS Read Short Response, 2 bytes Returned.

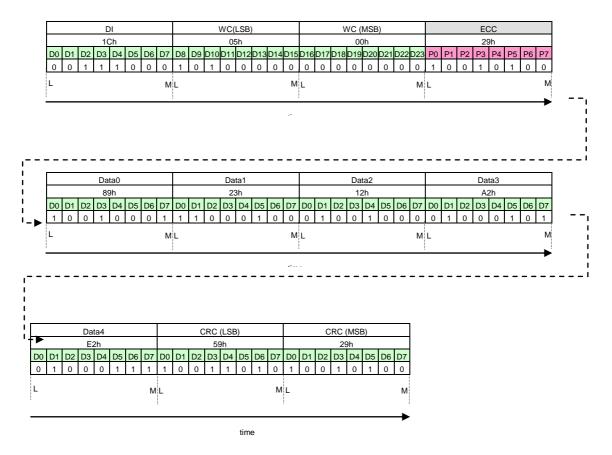

## 2.5 POWER SUPPLY SETTING SEQUENCE

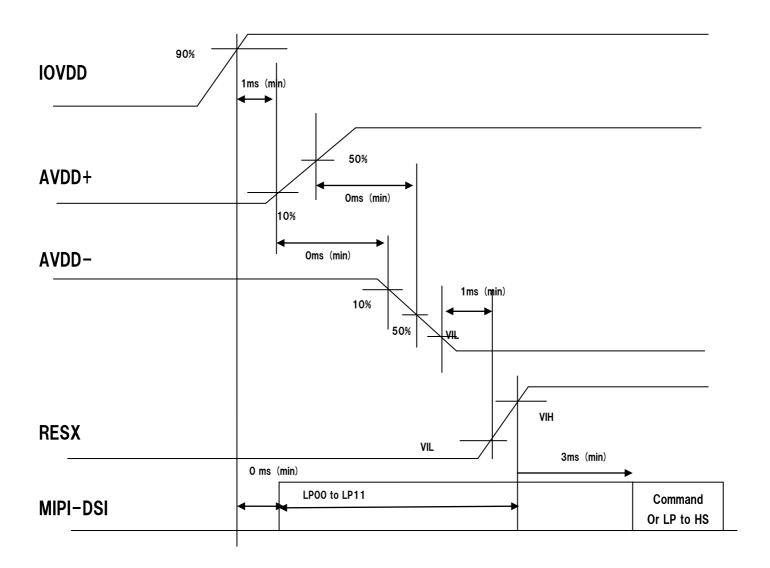

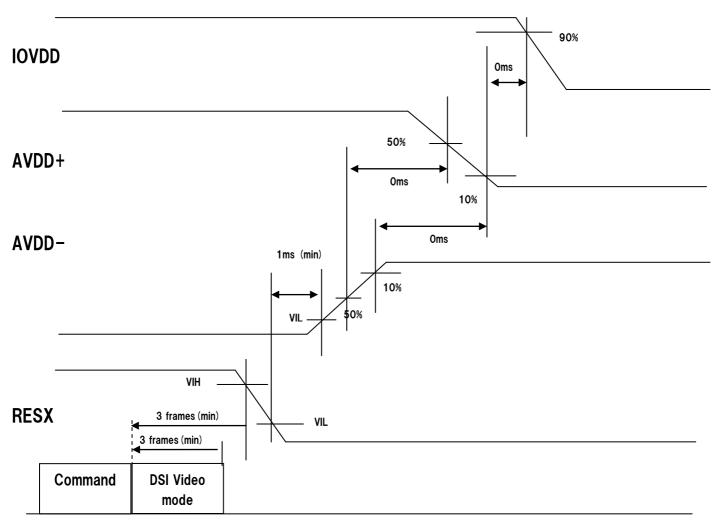

The power supply ON/OFF setting for Display ON/OFF, Sleep Set/Exit sequences is illustrated in figure below. When setting instruction to the R63311, the sequences shown in below figures must be followed to complete the instruction setting.

### 2.5.1 Power and Display on sequence.

## 2.5.2 Power and Display off sequence.

# 2.5.3 The waveform imaging of power on

Note: If the restriction of above power on sequence will not obeyed, there is possibility that the driver IC may be destroyed

# 2.5.4 The waveform image of power off sequence

If last command is "Sleep in" command(10h),DSI video mode signal should be kept output more than 3frame length.

Note: If the restriction of above power off sequence will not obeyed, there is possibility that the driver IC may be destroyed

### 2.6 COMMAND TABLE

### **Command Table 1**

| Address |                                   |                   |         |         |         |         |         |         |         |         |

|---------|-----------------------------------|-------------------|---------|---------|---------|---------|---------|---------|---------|---------|

| [Hex]   | Parameter                         | Instruction       | D7      | D6      | D5      | D4      | D3      | D2      | D1      | D0      |

| 00h     |                                   | NOP               |         |         |         | No Arg  | gument  |         |         |         |

| 01h     |                                   | SOFT_REST         |         |         |         | No Arg  | gument  |         |         |         |

|         | 1 <sup>st</sup> Parameter         |                   | ID1[15] | ID1[14] | ID1[13] | ID1[12] | ID1[11] | ID1[10] | ID1[9]  | ID1[8]  |

|         | 2 <sup>nd</sup> Parameter         |                   | ID1[7]  | ID1[6]  | ID1[5]  | ID1[4]  | ID1[3]  | ID1[2]  | ID1[1]  | ID1[0]  |

|         | 3 <sup>rd</sup> Parameter         |                   | ID2[15] | ID2[14] | ID2[13] | ID2[12] | ID2[11] | ID2[10] | ID2[9]  | ID2[8]  |

|         | 4 <sup>th</sup> Parameter         |                   | ID2[7]  | ID2[6]  | ID2[5]  | ID2[4]  | ID2[3]  | ID2[2]  | ID2[1]  | ID2[0]  |

| 0.45    | 5 <sup>th</sup> Parameter         |                   | ID3[7]  | ID3[6]  | ID3[5]  | ID3[4]  | ID3[3]  | ID3[2]  | ID3[1]  | ID3[0]  |

| 04h     | 6 <sup>th</sup> Parameter         | RDIDIF            | ID4[7]  | ID4[6]  | ID4[5]  | ID4[4]  | ID4[3]  | ID4[2]  | ID4[1]  | ID4[0]  |

|         | 7 <sup>th</sup> Parameter         |                   | 0       | IFID[6] | IFID[5] | IFID[4] | IFID[3] | IFID[2] | IFID[1] | IFID[0] |

|         | 8 <sup>th</sup> ~15 <sup>th</sup> |                   |         |         |         |         |         |         |         | •       |

|         | Parameter                         |                   | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

|         | 16 <sup>th</sup> Parameter        |                   | 1       | 1       | 1       | 1       | 1       | 1       | 1       | 1       |

| 05h     | 1 <sup>st</sup> Parameter         | RDNUMED           | D7      | D6      | D5      | D4      | D3      | D2      | D1      | D0      |

| 06h     | 1 <sup>st</sup> Parameter         | GET_RED_CHANNEL   | R7      | R6      | R5      | R4      | R3      | R2      | R1      | R0      |

| 07h     | 1 <sup>st</sup> Parameter         | GET_GREEN_CHANNEL | G7      | G6      | G5      | G4      | G3      | G2      | G1      | G0      |

| 08h     | 1 <sup>st</sup> Parameter         | GET_BLUE_CHANNEL  | B7      | B6      | B5      | B4      | B3      | B2      | B1      | B0      |

| 0Ah     | 1 <sup>st</sup> Parameter         | GET_POWER_MODE    | 0       | 0       | 0       | D4      | 1       | D2      | 0       | 0       |

| 0Bh     | 1 <sup>st</sup> Parameter         | GET_ADDRESS_MODE  | D7      | D6      | 0       | 0       | D3      | 0       | 0       | 0       |

| 0Ch     | 1 <sup>st</sup> Parameter         | GET_PIXEL_FORMAT  | 0       | D6      | D5      | D4      | 0       | 0       | 0       | 0       |

| 0Dh     | 1 <sup>st</sup> Parameter         | GET_DISPLAY_MODE  | 0       | 0       | D5      | 0       | 0       | D2      | D1      | D0      |

| 0Eh     | 1 <sup>st</sup> Parameter         | GET_SIGNAL_MODE   | D7      | D6      | 0       | 0       | 0       | 0       | 0       | D0      |

| 0Fh     | 1 <sup>st</sup> Parameter         | RDDSDR            | 0       | D6      | 0       | 0       | 0       | 0       | 0       | 0       |

| 10h     |                                   | ENTER_SLEEP_MODE  |         |         |         | No Arg  | gument  |         |         |         |

| 11h     |                                   | EXIT_SLEEP_MODE   |         | r       | r       | No Arg  | gument  | r       | r       |         |

| 26h     | 1 <sup>st</sup> Parameter         | GAMSET            | 0       | D6      | 0       | 0       | GC3     | GC2     | GC1     | GC0     |

| 28h     |                                   | SET_DISPLAY_OFF   |         |         |         | No Arg  | gument  |         |         |         |

| 29h     |                                   | SET_DISPLAY_ON    |         |         |         | No Arg  | gument  |         |         |         |