MODEL NO. : TM027CDH08

| ISSUED DAT              | E: <u>20</u>         | <u>10-07-23</u> |             |

|-------------------------|----------------------|-----------------|-------------|

| VERSION                 | : <u>Ve</u>          | r 1.0           |             |

|                         | minary Sp<br>Product |                 |             |

| Customer :              |                      | _               |             |

| Approved by             |                      |                 | Notes       |

|                         |                      |                 |             |

| SHANGHAI TIANMA Confirm | ed :                 |                 |             |

| Prepared by             | Check                | ed by           | Approved by |

|                         |                      |                 |             |

The information contained herein is the exclusive property of SHANGHAI TIANMA MICRO-ELECTRONICS Corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of SHANGHAI TIANMA MICRO-ELECTRONICS Corporation.

This technical specification is subjected to change without notice

# **Table of Contents**

| Co  | versheet                           | 1        |

|-----|------------------------------------|----------|

| Tab | ole of Contents                    | 2        |

| Re  | cord of Revision                   | 3        |

| 1   | General Specifications             | 4        |

| 2   | Input/Output Terminals             |          |

| 3   | Absolute Maximum Ratings           |          |

| 4   | Electrical Characteristics         | 7        |

| 5   | Timing Chart                       | <u>9</u> |

| 6   | Power On/Off Sequence              |          |

| 7   | Optical Characteristics            | 36       |

| 8   | Environmental / Reliability Tests  |          |

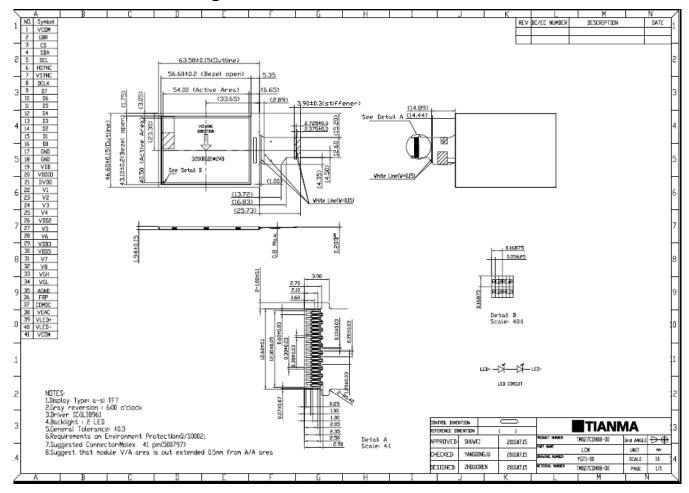

| 9   | Mechanical Drawing                 | 41       |

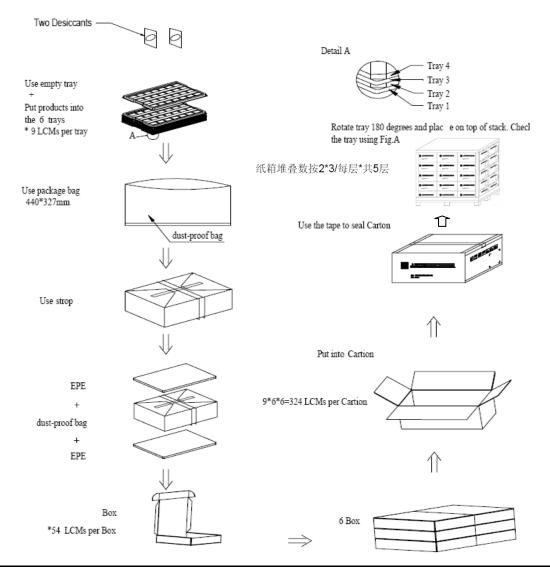

| 10  | Packing Drawing                    | 42       |

|     | Precautions For Use of LCD Modules |          |

|     |                                    |          |

# **Record of Revision**

| Rev | Issued Date | Description                       | Editor  |

|-----|-------------|-----------------------------------|---------|

| 1.0 | 2010-07-23  | Preliminary Specification Release | Huiwang |

|     |             |                                   |         |

|     |             |                                   |         |

|     |             |                                   |         |

|     |             |                                   |         |

|     |             |                                   |         |

|     |             |                                   |         |

|     |             |                                   |         |

|     |             |                                   |         |

|     |             |                                   |         |

|     |             |                                   |         |

|     |             |                                   |         |

|     |             |                                   |         |

|     |             |                                   |         |

|     |             |                                   |         |

|     |             |                                   |         |

|     |             |                                   |         |

|     |             |                                   |         |

|     |             |                                   |         |

|     |             |                                   |         |

# 1 General Specifications

|                               | Feature                         | Spec                                    |

|-------------------------------|---------------------------------|-----------------------------------------|

|                               | Size                            | 2.7 inch                                |

|                               | Resolution                      | 320RGBx240                              |

|                               | Interface                       | 8-bit RGB /8-bit Dummy RGB /CCIR656/601 |

|                               | Color Depth                     | 16.7M                                   |

|                               | Technology Type                 | a-Si                                    |

| Display Spec                  | Pixel pitch (mm)                | 0.16875x0.16875                         |

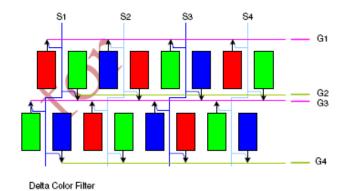

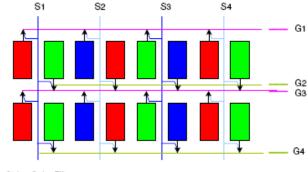

|                               | Pixel Configuration             | R.G.B. Delta                            |

|                               | Display Mode                    | TM With Normally White                  |

|                               | Surface Treatment(Up Polarizer) | HC                                      |

|                               | Viewing Direction               | 12 o'clock                              |

|                               | Gray Scale Inversion Direction  | 6 o'clock                               |

|                               | LCM (W x H x D) (mm)            | 63.50x46.60x1.94                        |

| Mashaniasi                    | Active Area(mm)                 | 54.0040.50                              |

| Mechanical<br>Characteristics | With /Without TSP               | Without TSP                             |

|                               | Weight (g)                      | TBD                                     |

|                               | LED Numbers                     | 2 LEDs                                  |

| Electronic                    | Driver IC                       | ILI8961                                 |

Note 1: Viewing direction for best image quality is different from TFT definition, there is a 180 degree shift.

Note 2: Requirements on Environmental Protection: RoHS

Note 3: LCM weight tolerance: +/- 5%

# 2 Input/Output Terminals

### 2.1 TFT LCD Panel

Matching Connector:

| No | Symbol | I/O | Description                                                            | Remark |

|----|--------|-----|------------------------------------------------------------------------|--------|

| 1  | VCOM   | I   | Panel common voltage                                                   |        |

| 2  | GRB    | I   | Global reset pin, it should be connected to VDDIO in normal operation. |        |

| 3  | CS     | I   | Data input Enable.                                                     |        |

| 4  | SDA    | 1   | SPI data input                                                         |        |

| 5  | SCL    | 1   | SPI clock input                                                        |        |

| 6  | HSYNC  | I   | Horizontal sync input                                                  |        |

| 7  | VSYNC  | 1   | Vertical sync input                                                    |        |

| 8  | DCLK   | 1   | Data clock input                                                       |        |

| 9  | D7     | I   | Data input; MSB                                                        |        |

| 10 | D6     | I   | Data input                                                             |        |

| 11 | D5     | I   | Data input                                                             |        |

| 12 | D4     | I   | Data input                                                             |        |

| 13 | D3     | I   | Data input                                                             |        |

| 14 | D2     | I   | Data input                                                             |        |

| 15 | D1     | I   | Data input                                                             |        |

| 16 | D0     | 1   | Data input; LSB                                                        |        |

| 17 | GND    | Р   | Power ground                                                           |        |

| 18 | GND    | Р   | Power ground                                                           |        |

| 19 | VDD    | Р   | Power supply for charge pump circuit.                                  |        |

| 20 | VDDIO  | Р   | Power supply for digital interface                                     |        |

| 21 | DVDD   | С   | Power setting capacitor connecting pin.                                |        |

| 22 | V1     | С   | Power setting capacitor connecting pin.                                |        |

| 23 | V2     | С   | Power setting capacitor connecting pin.                                | _      |

| 24 | V3     | С   | Power setting capacitor connecting pin.                                |        |

| 25 | V4     | С   | Power setting capacitor connecting pin.                                |        |

| 26 | VDD2   | С   | Power setting capacitor connecting pin.                                |        |

| _ | SHANGHAI | TIANI |

|---|----------|-------|

| TM <sub>0</sub> | 270  | DH | ng v | \/1 | n |

|-----------------|------|----|------|-----|---|

| I IVIU          | 21 G | υп | บด   | VI. | u |

| 27 | V5     | С | Power setting capacitor connecting pin. |  |

|----|--------|---|-----------------------------------------|--|

| 28 | V6     | С | Power setting capacitor connecting pin. |  |

| 29 | VDD3   | С | Power setting capacitor connecting pin. |  |

| 30 | VDD5   | С | Power setting capacitor connect pin     |  |

| 31 | V7     | С | Power setting capacitor connect pin     |  |

| 32 | V8     | Р | Power setting capacitor connect pin.    |  |

| 33 | VGH    | 0 | Power setting capacitor connect pin.    |  |

| 34 | VGL    | 0 | Power setting capacitor connect pin.    |  |

| 35 | AGND   | С | Ground for analog circuits.             |  |

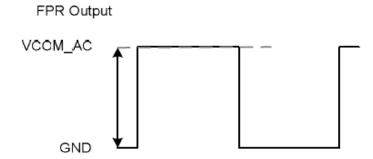

| 36 | FRP    | 0 | Frame polarity output for panel VCOM.   |  |

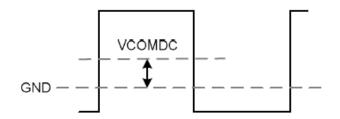

| 37 | VCOMDC | 0 | VCOM DC output.                         |  |

| 38 | VCAC   | 0 | Power setting capacitor for VCOM AC.    |  |

| 39 | LED+   | Р | LED power anode                         |  |

| 40 | LED-   | Р | LED power cathode                       |  |

| 41 | VCOM   | I | Panel common voltage                    |  |

Note2.1: I/O definition:

I--- Input; O---Output; P---Power/Ground; C---Capacitor; NC--- Not Connected

# 3 Absolute Maximum Ratings

### 3.1 Driving TFT LCD Panel

Ta = 25°C

| Item                          | Symbol                                               | Min  | Max           | Unit          | Remark           |

|-------------------------------|------------------------------------------------------|------|---------------|---------------|------------------|

| Supply Voltage                | VDD                                                  | -0.3 | 5.0           | ٧             |                  |

| Input Signal Voltage          | D0~D7,VCOM,GRB,CS,SDA,SCL,<br>HSYNC, VSYNC,DCLK,VCOM | -0.3 | VDDIO<br>+0.3 | ٧             |                  |

| Back Light Forward<br>Current | I <sub>LED</sub>                                     | -    | 30            | mA            | 2 LEDs in series |

| Operating Temperature         | T <sub>OPR</sub>                                     | -20  | 70            | ${\mathbb C}$ |                  |

| Storage Temperature           | T <sub>STG</sub>                                     | -30  | 80            | $^{\circ}$    |                  |

### 4 Electrical Characteristics

### 4.1 Driving TFT LCD Panel

GND=0V, Ta=25°C

| Item                             |               | Symbol          | MIN        | TYP    | MAX       | Unit | Remark                |

|----------------------------------|---------------|-----------------|------------|--------|-----------|------|-----------------------|

| Supply Vol                       | tage          | VDD             | 3.0        | 3.3    | 3.6       | V    |                       |

|                                  | High          | VIH             | 0.7xVDDIO  | -      | VDDIO     | V    | VDDIO =<br>2.7V~3.6V  |

| Input<br>Signal                  | Level         | VIII            | 0.8xVDDIO  | -      | VDDIO     | V    | VDDIO =<br>1.65V~2.7V |

| Voltage                          | Low           | VIL             | GND        | -      | 0.3xVDDIO | V    | VDDIO =<br>2.7V~3.6V  |

|                                  | Level         | VIL             | GND        | -      | 0.2xVDDIO | V    | VDDIO =<br>1.65V~2.7V |

| Output<br>Signal                 | High<br>Level | VOH             | VDDIO -0.4 | -      | VDDIO     | V    | VGH,VGL,FRP,          |

| Voltage                          | Low<br>Level  | VOL             | GND        | -      | 0.4       | V    | VCOMDC, VCAC          |

| (Panel+LSI)<br>Power Consumption |               | Normal<br>Mode  | -          | (16.0) | 1         | mA   | CLK 27MHz             |

|                                  |               | -               | -          | -      | -         | -    |                       |

|                                  |               | Standby<br>Mode | -          | (120)  | -         | uA   |                       |

### 4.2 Driving Backlight

Ta=25°C

| Item              | Symbol         | Min | Тур   | Max | Unit | Remark                    |

|-------------------|----------------|-----|-------|-----|------|---------------------------|

| Forward Current   | I <sub>F</sub> |     | 25    |     | mA   | E                         |

| Forward Voltage   | $V_{F}$        |     | (6.4) |     | V    | For one LED<br>Note 1,2,3 |

| Power Consumption | $W_{BL}$       | -   | 128   |     | mW   | 14010 1,2,0               |

Note 1: The figure below shows the connection of backlight LED.

Note 2: One LED: I<sub>F</sub> =25mA; Two LED:VF=6.4V

Note 3: The life of LED: 20,000 hours

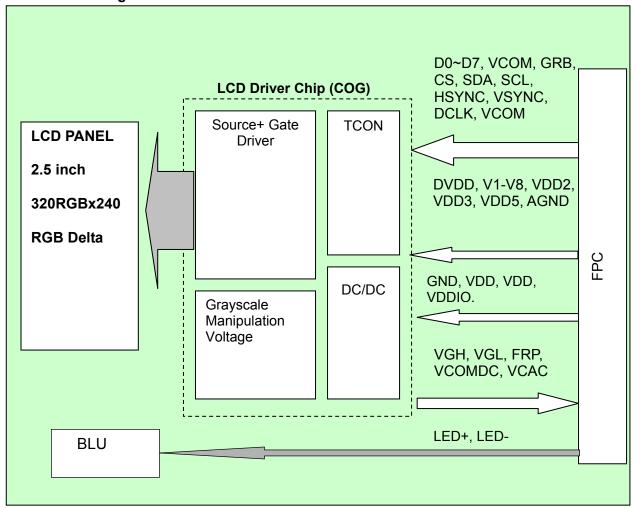

### 4.3 Block Diagram

# 5 Timing Chart

### 5.1 3-WIRE SERIAL CONTROL INTERFACE

### 5.2 3-WIRE REGISTER TABLE

| Register                                                                | Do             |

|-------------------------------------------------------------------------|----------------|

| Rooh   0   1/0   0   0   0   0   0   0   0   0   0                      |                |

| R03h                                                                    |                |

| R04h 0 1/0 0 0 0 1 0 0 Narrow C656_EN IF_SEL NP_SEL LDIF (10) (10) (10) |                |

| Ro4h 0 1/0 0 0 0 1 0 0 Narrow C656_EN IF_SEL NP_SEL LDIF (10) (10)      |                |

|                                                                         | YDIR<br>(1)    |

| R05h 0 1/0 0 0 0 1 0 1 DRV_SET GRB PWM_SEL VGHL_EN PWM_                 |                |

| Bosh 0 1/0 0 0 1 1 0 HBLK_EN FB_SEL VBLK                                |                |

| P07b 0 1/0 0 0 1 1 1 1 1 HBLK                                           |                |

| R08h 0 1/0 0 0 1 0 0 DRV_SEL                                            | ×              |

| PoPh 0 1/0 0 0 1 0 1 1 REGSEL V V V V V V V V V V V V V V V V V V V     | ×              |

| ROCH 0 1/0 0 0 1 1 0 0 VST DE_EN CbCr DENP VSDP HSD                     | CLKINP         |

| RODH 0 1/0 0 0 1 1 0 1 CONTRAST                                         | (0)            |

| (40h)                                                                   |                |

| (40h)                                                                   |                |

| ROFI   0   70   0   1   1   1   X   (40h)                               |                |

| (40h)                                                                   |                |

| R11h 0 1/0 0 1 0 0 0 1 x                                                |                |

| H12h   0   1/0   0   1   0   0   1   0   0   1   0   (00)               |                |

| R16h 0 1/0 0 1 0 1 1 0 x x x x x GOP_EN x                               | x              |

| R17h 0 1/0 0 1 0 1 1 1 1 x L016P_SEL x L008P_S (100)                    |                |

| R18h 0 1/0 0 1 1 0 0 0 x L050P_SEL x L032P_S (101)                      |                |

| R19h 0 1/0 0 1 1 0 0 1 x L096P_SEL x L072P_S (100)                      | EL             |

| R1Ah 0 1/0 0 1 1 0 1 0 x L120P_SEL x L110P_S (101)                      | EL             |

| R2Bh 0 1/0 1 0 1 0 1 1 x x X X X X X X X                                | STB<br>(0)     |

| R2Fh 0 1/0 1 0 1 1 1 1 x VGH_SEL CF_SEL LC_SEL (11) (0) (00)            | SOPC<br>(01)   |

| P3Ch 0 1/0 1 1 1 1 0 0 GAMMA_EN L127P_SEL L000P_S                       |                |

| NSSN 0 10 1 1 1 0 0 (0) (011)                                           |                |

| R3Dh   0   1/0   1   1   1   0   1   X   L127N_SEL   X   L000N_S (111)  | EL             |

| R3Eh 0 1/0 1 1 1 1 1 0 X L016N_SEL X L008N_S (100)                      | EL             |

| R3Fh 0 1/0 1 1 1 1 1 X L050N_SEL X L032N_S (100)                        | EL             |

| R40h 1 1/0 0 0 0 0 0 0 X L096N_SEL X L072N_S (011)                      | EL             |

| R41h 1 1/0 0 0 0 0 0 1 X L120N_SEL X L110N_S (100)                      | EL             |

| R55h 1 1/0 0 1 0 1 0 1 x INV_SEL DAT_INV x x x                          | х              |

| R57h 1 1/0 0 1 0 1 1 1 VGHL_ENB x x x X X X X                           | х              |

|                                                                         | GL_SEL<br>(10) |

Note:

- 1. When RSTB is low, all registers reset to default values.

- 2. Serial commands are executed at next VSD signal.

### 5.3 3-WIRE REGISTER DESCRIPTION

VCAC (R00h[3:0]): VCOM voltage AC level seletion

| D[3:0] |   |   |   | Low Voltage LC(V) | Normal Voltage<br>LC1(V) | Normal Voltage<br>LC 2(V) |

|--------|---|---|---|-------------------|--------------------------|---------------------------|

| 0      | 0 | 0 | 0 | 3.6               | 4.0                      | 5.0                       |

| 0      | 0 | 0 | 1 | 3.7               | 4.1                      | 5.1                       |

| 0      | 0 | 1 | 0 | 3.8               | 4.2                      | 5.2                       |

| 0      | 0 | 1 | 1 | 3.9               | 4.3                      | 5.3                       |

| 0      | 1 | 0 | 0 | 4                 | 4.4                      | 5.4                       |

| 0      | 1 | 0 | 1 | 4.1               | 4.5                      | 5.5                       |

| 0      | 1 | 1 | 0 | 4.2 (default)     | 4.6 (default)            | 5.6 (default)             |

| 0      | 1 | 1 | 1 | 4.3               | 4.7                      | 5.7                       |

| 1      | 0 | 0 | 0 | 4.4               | 4.8                      | 5.8                       |

| 1      | 0 | 0 | 1 | 4.5               | 4.9                      | 5.9                       |

| 1      | 0 | 1 | 0 | 4.6               | 5.0                      | 6.0                       |

| 1      | 0 | 1 | 1 | 4.7               | 5.1                      | 6.1                       |

| 1      | 1 | Х | Х | 4.8               | 5.2                      | 6.2                       |

\*Note: Please reference LC type to R2Fh[3:2] LC\_SEL

### C601\_EN (R00h[6]): CCIR601 interface control

| D6 | Function                                                                         |

|----|----------------------------------------------------------------------------------|

| 0  | Disable CCIR601. (default)                                                       |

| 1  | Enable CCIR601. (please refer to the table of R04H(IF_SEL) for detail descrption |

### Y CbCr (R00h[7]): Y & CbCr exchange position (only valid for 8-bit input YUV640/YUV720)

|           | Under $R0C[4]$ CbCr = '0'   | Under R0C [4] CbCr = '1'    |

|-----------|-----------------------------|-----------------------------|

| D7 = '0'  | Cb0 Y0 Cr0 Y1 Cb2 Y2 Cr2 Y3 | Cr0 Y0 Cb0 Y1 Cr2 Y2 Cb2 Y3 |

| (default) |                             |                             |

TM027CDH08 V1.0

D7 = '1'

| Y0 Cb0 Y1 Cr0 Y2 Cb2 Y3 C | Cr2 |

|---------------------------|-----|

|---------------------------|-----|

| Parameter Data |        |                         |       |  |  |  |  |  |

|----------------|--------|-------------------------|-------|--|--|--|--|--|

| Register       | D7     | D7 D6 D5 D4 D3 D2 D1 D0 |       |  |  |  |  |  |

| R01h           | VCDCEN | v                       | VCDC  |  |  |  |  |  |

| 110111         | (1)    | ^                       | (21h) |  |  |  |  |  |

### VCDC (R01h[5:0]): VCOM voltage DC level selection (20mV/step)

| D[5:0] | Low Voltage LC(V) | Normal Voltage LC 1 & 2(V) |

|--------|-------------------|----------------------------|

| 00h    | 0.24              | 0.5                        |

| :      | :                 | :                          |

| 21h    | 0.90 (default)    | 1.16 (default)             |

| :      | :                 | :                          |

| 3Fh    | 1.5               | 1.76                       |

VCOMDC couple by FRP

### VCDCEN (R01h[7]): VCOM DC enables control

| D7 | VCDCEN Fuction                                                                  |

|----|---------------------------------------------------------------------------------|

| 0  | VCOM DC function disabled. The VCOMDC pin is connected to GND.                  |

| 1  | VCOM DC function enabled. The VCOMDC voltage follows VCOM DC setting. (default) |

| Pogietor | Parameter Data          |  |  |  |  |  |    |  |  |

|----------|-------------------------|--|--|--|--|--|----|--|--|

| Register | D7 D6 D5 D4 D3 D2 D1 D0 |  |  |  |  |  | D0 |  |  |

| R03h     | Brightness<br>(40h)     |  |  |  |  |  |    |  |  |

### Brightness (R03h[7:0]): RGB brightness level control

| D[7:0] | Brightness Offset      |

|--------|------------------------|

| 00h    | Dark. (-64)            |

| 40h    | Center. (0). (default) |

| FFh    | Bright. (+191)         |

Setting accuracy 1bit/step

### TM027CDH08 V1.0

| Dogiotor | Parameter Data |         |        |    |      |     |      |      |  |

|----------|----------------|---------|--------|----|------|-----|------|------|--|

| Register | D7             | D6      | D5     | D4 | D3   | D2  | D1   | D0   |  |

| R04h     | Narrow         | C656_EN | IF_SEL |    | NP_S | SEL | LDIR | YDIR |  |

| NO4II    | (0)            | (0)     | (00)   |    | (10) |     | (1)  | (1)  |  |

### YDIR(R04h[0]): Source driver output direction selection

|   | YDIR Function                                               |

|---|-------------------------------------------------------------|

| 0 | Shift from right to left. Y1 ←Y2←←Y959←Y960                 |

| 1 | Shift from left to right. Y1 → Y2 → → Y959 → Y960 (default) |

### LDIR(R04h[1]): Gate driver output direction selection

|   | LDIR Function                                     |

|---|---------------------------------------------------|

| 0 | Shift from down to up. L1 ←L2←←L239←L240          |

| 1 | Shift from up to down. L1→L2→→L239→L240 (default) |

### NP\_SEL[1:0] (R04h[3:2]): NTSC/PAL input mode selection.

| D[3 | :2] | NTSC/PAL Mode             |

|-----|-----|---------------------------|

| 0   | 0   | PAL.                      |

| 0   | 1   | NTSC                      |

| 1   | X   | Auto detection. (default) |

### IF\_SEL[1:0] (R04h[5:4]): Input data format selection.

| R00h[6] | D6 | D[5 | 5:4] | Input Timing format       |

|---------|----|-----|------|---------------------------|

| 0       | 0  | 0   | 0    | 8-bit RGB. (default)      |

| 0       | 0  | 0   | 1    | 8-bit Dummy RGB 320 x 240 |

| 0       | 0  | 1   | Х    | 8-bit Dummy RGB 360 x 240 |

| 0       | 1  | X   | Х    | CCIR656                   |

| 1       | 1  | 0   | Х    | YUV640                    |

| 1       | 1  | 1   | 0    | YUV720                    |

### C656\_EN(R04h[6]): CCIR656/CCIR601 or RGB/RGB-Dummy input interface selection.

|    | • • •                       |

|----|-----------------------------|

| D6 | Data format                 |

| 0  | RGB input. (default)        |

| 1  | CCIR656/YUV640/YUV720 input |

### Narrow(R04h[7]): Normal / Narrow display selection

| D7 | Function                  |

|----|---------------------------|

| 0  | Normal display. (default) |

| 1  | Narrow display.           |

Narrow = 0

Narrow = 1

Int \*Not valid for parallel and serial 8-bit RGB interface.

;s

permission of SHANGHAI TIANMA MICRO-ELECTRONICS Corporation.

### TM027CDH08 V1.0

| Pogietor | Parameter Data |     |                    |    |    |         |        |    |

|----------|----------------|-----|--------------------|----|----|---------|--------|----|

| Register | D7             | D6  | D5                 | D4 | D3 | D2      | D1     | D0 |

| R05h     | DRV_SET        | GRB | PWM_SEL            |    |    | VGHL_EN | PWM_EN | v  |

| HUSII    | (0)            | (1) | (0 <del>11</del> ) |    |    | (1)     | (1)    | X  |

### PWM\_EN(R05h[1]): Back light power converter control.

| D1 | PWM_EN Funciton                                                                        |

|----|----------------------------------------------------------------------------------------|

| 0  | The back light power converter is off.                                                 |

| 1  | The back light power converter is controlled by STB's power on/off sequence. (default) |

### VGHL\_EN(R05h[2]): VGH/VGL charge pump control

| D2 | VGHL_EN Funciton                                                            |

|----|-----------------------------------------------------------------------------|

| 0  | VGH/VGL charge pump is always off.VGL will set to GND level.                |

| 1  | VGH/VGL charge pump is controlled by STB's power on/off sequence. (default) |

### PWM\_SEL(R05h[5:3]): PWM duty cycle selection for back light power convert

|   | D[5:3] |   | PWM duty cycle |

|---|--------|---|----------------|

| 0 | 0      | 0 | 55%            |

| 0 | 0      | 1 | 60%            |

| 0 | 1      | 0 | 65%            |

| 0 | 1      | 1 | 70% (default)  |

| 1 | 0      | 0 | 75%            |

| 1 | 0      | 1 | 80%            |

| 1 | 1      | 0 | 85%            |

| 1 | 1      | 1 | 90%            |

### GRB(R05h[6]): Global reset

| D6 | GRB Function                          |

|----|---------------------------------------|

| 0  | Reset all registers to default value. |

| 1  | Normal operation. (default)           |

### DRV\_SET(R05h[7]): DRV signal frequency selection

| D7 | DRV operation frequency   |

|----|---------------------------|

| 0  | High Frequency. (default) |

| 1  | Low Frequency.            |

### TM027CDH08 V1.0

| Pogletor | Parameter Data |               |     |      |    |       |    |    |

|----------|----------------|---------------|-----|------|----|-------|----|----|

| Register | D7             | D6            | D5  | D4   | D3 | D2    | D1 | D0 |

| R06h     | HBLK_EN        | BLK_EN FB_SEL |     | VBLK |    |       |    |    |

| HUUII    | (0)            | (0            | 00) |      |    | (15h) |    |    |

### VBLK[4:0]( R06h[4:0]): Vertical blanking setting for 8-bit RGB, 8-bit Dummy RGB & CCIR656

For 8-bit RGB, 8-bit Dummy RGB, YUV640, YUV720, CCIR656 NTSC mode, and Parallel RGB input mode.

| D[4:0]  | VBLK Function | Unit |

|---------|---------------|------|

| 00h~03h | 3.            |      |

| 04h     | 4.            | н    |

| 15h     | 21. (default) | "    |

| 1Fh     | 31.           |      |

For 8-bit Dummy RGB, YUV640, YUV720, CCIR656 PAL mode (Vertical Blanking + 3)

| D[4:0] | VBLK Function | Unit |

|--------|---------------|------|

| 00h    | 3.            |      |

| 04h    | 7.            | — н  |

| 15h    | 24. (default) | П    |

| 1Fh    | 34.           |      |

### FB SEL[1:0] (R06h[6:5]): adjustable for DC-DC feedback threshold voltage

| D[6:5] | Feedback Threshold Voltage |

|--------|----------------------------|

| 00     | 0.6 V. (default)           |

| 01     | 0.75V.                     |

| 10     | 0.45V.                     |

| 11     | 0.3V.                      |

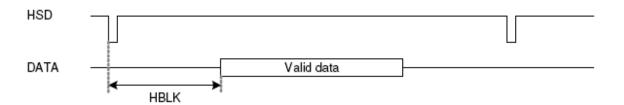

### HBLK\_EN (R06h[7]): Horizontal blanking function enable control

| D[7] | HBLK EN Function |

|------|------------------|

| 0    | Disable(default) |

| 1    | Enable           |

| Pogletor | Parameter Data |    |    |    |    |    |    |    |  |

|----------|----------------|----|----|----|----|----|----|----|--|

| Register | D7             | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |

| R07h     | HBLK<br>(46h)  |    |    |    |    |    |    |    |  |

| NO/II    |                |    |    |    |    |    |    |    |  |

### HBLK (R07h[7:0]): Horizontal blanking setting

| HBLK_EN | D7~D0   | HBLK   | Unit     | NTSC/PAL Mode   |  |

|---------|---------|--------|----------|-----------------|--|

| X       | 32h~45h | 50~69  |          |                 |  |

| X       | 46h     | 70     | CLKIN(*) | 8-bit RGB       |  |

| X       | 47h∼FFh | 71~255 |          |                 |  |

| X       | X       | 241    | CLKIN(*) | 8-bit Dummy RGB |  |

| 0       | XXh     | 240    | CLKIN(*) |                 |  |

| 1       | 00h~03h | 3      | CLKIN(*) | YUV640, YUV720  |  |

| 1       | 04h~FFh | 4~255  | CLKIN()  |                 |  |

| 0       | X       | 61     |          |                 |  |

| 1       | 00h~03h | 3      | CLKIN(*) | Parallel RGB    |  |

|         | 04h~3Fh | 4~63   | , ,      |                 |  |

<sup>\*</sup>The frequency of CLKIN is different under different input timing.

'X': don't care

### TM027CDH08 V1.0

| Pogletor | Parameter Data |          |    |    |    |    |    |    |  |

|----------|----------------|----------|----|----|----|----|----|----|--|

| Register | D7             | D6       | D5 | D4 | D3 | D2 | D1 | D0 |  |

| R08h     | DRV_9<br>(00   | SEL<br>) | х  | ×  | x  | х  | х  | х  |  |

### DRV\_SEL(R08h[7:6]): Backlight driving capability setting

| D7 | D6 | DRV_SEL capability             |

|----|----|--------------------------------|

| 0  | 0  | Normal capability. (default)   |

| 0  | 1  | 2 times the Normal capability. |

| 1  | 0  | 3 times the Normal capability. |

| 1  | 1  | 4times the Normal capability.  |

|   | Register | Parameter Data |    |            |    |    |    |    |    |  |

|---|----------|----------------|----|------------|----|----|----|----|----|--|

| l | negistei | D7             | D6 | <b>D</b> 5 | D4 | D3 | D2 | D1 | D0 |  |

|   | R0Bh     | REGSEL<br>(0)  | х  | х          | х  | х  | x  | х  | х  |  |

### REGSEL (R0Bh[7]): MTP function control register

| D7 | REGSEL Function                                                     |

|----|---------------------------------------------------------------------|

| 0  | VCOMDC Output Voltage is read from MTP memory. (default)            |

| 1  | VCOMDC Output Voltage is controlled by the register R01h_VCDC[5:0]. |

### TM027CDH08 V1.0

|   | Register | Parameter Data         |    |              |             |             |             |             |               |  |  |

|---|----------|------------------------|----|--------------|-------------|-------------|-------------|-------------|---------------|--|--|

| 1 | negistei | D7                     | D6 | D5           | D4          | D3          | D2          | D1          | D0            |  |  |

|   | R0Ch     | VS <sup>-</sup><br>(00 |    | DE_EN<br>(0) | CbCr<br>(0) | DENP<br>(0) | VSDP<br>(1) | HSDP<br>(1) | CLKINP<br>(0) |  |  |

### CLKINP (R0Ch[0]): CLKIN polarity selection

|   | CLKINP Function                            |

|---|--------------------------------------------|

| 0 | Latch data at CLKIN rising edge. (default) |

| 1 | Latch data at CLKIN falling edge           |

### HSDP (R0Ch[1]): HSD polarity selection

| D1 | HSDP Function                |

|----|------------------------------|

| 0  | Positive polarity.           |

| 1  | Negative polarity. (default) |

### VSDP (R0Ch[2]): VSD polarity selection

| D2 | VSDP Function                |

|----|------------------------------|

| 0  | Positive polarity.           |

| 1  | Negative polarity. (default) |

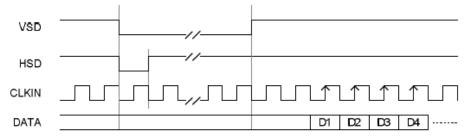

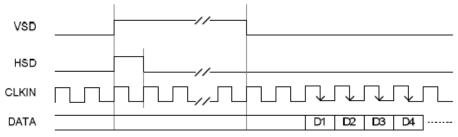

### HSDP = 1, VSDP = 1, CLKINP = 0

### HSDP = Q, VSDP = Q, CLKINP = 1.

### DENP (R0Ch[3]): DEN polarity selection

| -  |                             |

|----|-----------------------------|

| D3 | DENP Function               |

| 0  | Positive polarity (default) |

| 1  | Negative polarity           |

### CbCr (R0Ch[4]): Cb & Cr exchange position (valid for CCIR656 and YUV640/YUV720)

| D4 | CbCr Function      |

|----|--------------------|

| 0  | Cb→Y→Cr. (default) |

| 1  | Cr→Y→Cb.           |

### DE\_EN(R0Ch[5]) : DE mode selection

| D5 | DE_EN Function              |

|----|-----------------------------|

| 0  | HV mode selected. (default) |

| 1  | DE mode selected.           |

<sup>\*</sup> DE\_EN only controls the HV and DE mode at 8-bit RGB, 8-bit Dummy RGB and Parallel Mode.

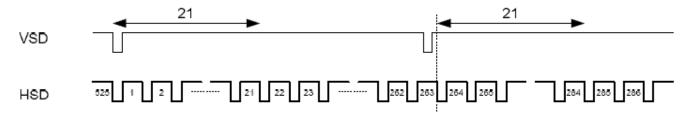

### VST(R0Ch[7:6]): Vertical start time of odd/even frame

8-bit RGB / 8-bit Dummy RGB NTSC / 8-bit Dummy RGB PAL(\*)

Parallel RGB input mode (PSEL= "Low")

| VS | VST VBLK |                  |           |  |

|----|----------|------------------|-----------|--|

| D7 | D6       | ODD/EVEN         | Unit      |  |

| X  | 0        | 21/21. (default) | H(Line)   |  |

| X  | 1        | 21/20.           | TI(LITIE) |  |

### CCIR656/YUV640/YUV720 NTSC/PAL(\*\*)

| V     | ST | VBLK             | Unit    |  |

|-------|----|------------------|---------|--|

| D7 D6 |    | ODD/EVEN         | Offic   |  |

| 0     | 0  | 21/21. (default) |         |  |

| 0     | 1  | 21/22            | ∐/Lipo\ |  |

| 1     | 0  | 22/21            | H(Line) |  |

| 1     | 1  | 22/22            |         |  |

- (\*) The typical value of VBLK of 8-bit Dummy RGB PAL (24 H) is different from 8-bit RGB/8-bit Dummy RGB NTSC(21H).

- (\*\*) The typical value of VBLK of CCIR656 PAL (24 H) is different from CCIR656 NTSC (21H).

Note: V-Blanking must be adjusted base on the input data.

### For example:

### TM027CDH08 V1.0

| Register | Parameter Data |    |    |    |      |    |    |    |

|----------|----------------|----|----|----|------|----|----|----|

|          | D7             | D6 | D5 | D4 | D3   | D2 | D1 | D0 |

| R0Dh     | CONTRAST       |    |    |    |      |    |    |    |

| RODE     |                |    |    | (4 | l0h) |    |    |    |

CONTRAST(R0Dh[7:0]): RGB contrast level setting, the gain changes(1/64)/bit.

### Gain formula=0.75+(R CONT/256)

| Contrast Gain |

|---------------|

| 0             |

|               |

| 1 (default)   |

|               |

| 3.984         |

|               |

| Pogletor |    |    |    | Parame | eter Data       |    |    |    |

|----------|----|----|----|--------|-----------------|----|----|----|

| Register | D7 | D6 | D5 | D4     | D3              | D2 | D1 | D0 |

| ROEh     | х  |    |    |        | R_CONT<br>(40h) |    |    |    |

R-CONT(R0Eh[6:0]): Red sub-pixel contrast level setting, the gain changes (1/256)/bit.

### Gain formula=0.75+(R\_CONT/256)

| D[6:0] | R Contrast Gain |

|--------|-----------------|

| 00h    | 0.75            |

|        |                 |

| 40h    | 1 (default)     |

|        |                 |

| 7Fh    | 1.246           |

| Register | Parameter Data |    |                   |    |    |    |    |    |  |

|----------|----------------|----|-------------------|----|----|----|----|----|--|

|          | D7             | D6 | D5                | D4 | D3 | D2 | D1 | D0 |  |

| R0Fh     | х              |    | R_BRIGHT<br>(40h) |    |    |    |    |    |  |

R-BRIGHT(R0Fh[6:0]): Red sub-pixel brightness level setting, setting accuracy: 1 step/bit.

| D[6:0] | R Brightness Offset  |

|--------|----------------------|

| 00h    | darker (-64)         |

|        |                      |

| 40h    | center (0) (default) |

|        |                      |

| 7Fh    | brighter (+63)       |

### TM027CDH08 V1.0

| Pogletor | Parameter Data       |  |  |    |     |  |    |  |

|----------|----------------------|--|--|----|-----|--|----|--|

| Register | D7 D6 D5 D4 D3 D2 D1 |  |  |    |     |  | D0 |  |

| R12h     |                      |  |  | TR | MEN |  |    |  |

| NIZII    |                      |  |  | (  | 00) |  |    |  |

### TRMEN (R12h): VCOM DC Trim Function Control Register

VCOMDC Trim function control register, Write the follow command sequentially to enable the VCOMDC trim function.

Adjust VCDC level:

Set TRMEN[7:0] = 00h and set REGSEL=1(R0Bh=80h)

Write proper VCDC[5:0] value using 3-wire command.

Programming the VCDC value into MTP memory:

Set VPP\_MTP = 7.5V with external power supply for programming operation. (Requirement)

Set TRMEN[7:0] as following sequence: A0h → 5Fh → EEh →00h

REGSEL will be clear to 0 after the programming procedure.

### Procedure-1 Set RoGSoL = 1, Please make sure VCDCoN=1

Procedure-2

Update VCDC vaule

# Procedure-3 VCOMDC trim state please follow Note

Procedure-4

Handware clear RoGSoL=0,

check RoGSoL =0 by 3-wire

read check VCOMDC value

# TRMoN≠A0h TRMoN=A0h TRMoN=A0h TRMoN=5Fh S1 TRMoN=ooh S2 TRMoN=00h Programming VCOM\_DC Value

### Note:

- The Trim Block can be writing for only "3" times

- 2. After finishing TRMEN command do not power off within 1 second.

- 3. Trim command exceed the limitation may cause the VCOMDC output unknown value.

The 4. The CLKIN input frequency should be 26MHz ~ 30MHz.

CS ten

Co permission of SHANGHAI TIANMA MICRO-ELECTRONICS Corporation.

### TM027CDH08 V1.0

| Pogletor |    | Parameter Data |    |    |    |               |    |    |  |

|----------|----|----------------|----|----|----|---------------|----|----|--|

| Register | D7 | D6             | D5 | D4 | D3 | D2            | D1 | D0 |  |

| R16h     | х  | х              | х  | ×  | х  | GOP_EN<br>(1) | х  | х  |  |

### GON\_EN (R16h): Select auto or manual gamma setting

| D2 | Gamma op enable Function        |

|----|---------------------------------|

| 0  | Manual set gamma by R17h~R1Ah.  |

| 1  | Auto set to gamma2.2. (default) |

| Pogletor |    |                    |                    | Parame |    |                    |    |    |

|----------|----|--------------------|--------------------|--------|----|--------------------|----|----|

| Register | D7 | D6                 | D5                 | D4     | D3 | D2                 | D1 | D0 |

| R17h     | х  | L016P_SEL<br>(101) |                    |        | х  | L008P_SEL<br>(100) |    |    |

| R18h     | х  |                    | L50P_ŚEL<br>(101)  |        |    | L032P_SEL<br>(100) |    |    |

| R19h     | х  | L096P_SEL<br>(100) |                    |        | х  |                    |    |    |

| R1Ah     | х  |                    | L120P_SEL<br>(101) |        | х  | L110P_SEL<br>(100) |    |    |

Registers: R17h~R1Ah

L008P\_SEL: Gamma op output selection to level VP8; L016P\_SEL: Gamma op output selection to level VP16; L032P\_SEL: Gamma op output selection to level VP32;

L050P\_SEL: Gamma op output selection to level VP50;

L072P\_SEL: Gamma op output selection to level VP72;

L096P\_SEL: Gamma op output selection to level VP96;

L110P\_SEL: Gamma op output selection to level VP110;

L120P\_SEL: Gamma op output selection to level VP120;

| Reference point | 000  | 001  | 010  | 011     | 100     | 101     | 110  | 111     |

|-----------------|------|------|------|---------|---------|---------|------|---------|

| L008P(100)      | -4△V | -3△V | -2△V | -△V     | Default | +△V     | +2△V | +3△V    |

| L016P(101)      | -5△V | -4△V | -3△V | -2△V    | -△V     | Default | +△V  | +2△V    |

| L032P(100)      | -4△V | -3△V | -2△V | -△V     | Default | +△V     | +2△V | +3△V    |

| L050P(101)      | -5△V | -4△V | -3△V | -2△V    | -△V     | Default | +△V  | +2△V    |

| L072P(011)      | -3△V | -2△V | -△V  | Default | +△V     | +2△V    | +3△V | +4△V    |

| L096P(100)      | -4△V | -3△V | -2△V | -△V     | Default | +△V     | +2△V | +3 \\ \ |

| L110P(100)      | -4△V | -3△V | -2△V | -△V     | Default | +△V     | +2△V | +3 △ V  |

| L120P(101)      | -5△V | -4△V | -3△V | -2△V    | -△V     | Default | +△V  | +2△V    |

Note:(1) For Low Voltage LC application, △V= 25mV ∘

(2) For Normal Voltage LC application, △V= 40mV ∘

### TM027CDH08 V1.0

| Pogletor |    | Parameter Data |    |    |    |    |    |            |

|----------|----|----------------|----|----|----|----|----|------------|

| Register | D7 | D6             | D5 | D4 | D3 | D2 | D1 | D0         |

| R2Bh     | х  | х              | х  | х  | х  | х  | х  | STB<br>(0) |

### STB(R2Bh[0]): Standby (Power saving) mode control

| D0 | STB Function            |

|----|-------------------------|

| 0  | Standby Mode. (default) |

| 1  | Normal operation.       |

| Register | Parameter Data |                 |    |               |                |    |          |    |

|----------|----------------|-----------------|----|---------------|----------------|----|----------|----|

| negistei | D7             | D6              | D5 | D4            | D3             | D2 | D1       | D0 |

| R2Fh     | х              | VGH_SEL<br>(11) |    | CF_SEL<br>(0) | LC_SEL<br>(00) |    | SP<br>(0 |    |

### SOPC (R2Fh[1:0]): Source output driving capability selection

| D1 | D0 | Source Driver Capability |

|----|----|--------------------------|

| 0  | 0  | -25%.                    |

| 0  | 1  | Normal. (default)        |

| 1  | 0  | +25%                     |

| 1  | 1  | +50%                     |

### LC\_SEL (R2Fh[3:2]): Source output driving capability selection

| D3 | D2 | LC type selection        |

|----|----|--------------------------|

| 0  | 0  | Low Voltage LC (default) |

| 0  | 1  | -                        |

| 1  | 0  | Normal Voltage LC 2      |

| 1  | 1  | Normal Voltage LC 1      |

### CF\_SEL(R2Fh[4]): Color filter selection

| D4 | Function                      |

|----|-------------------------------|

| 0  | Delta color filter. (default) |

| 1  | Stripe color filter.          |

Stripe Color Filter

### TM027CDH08 V1.0

VGH\_SEL(R2Fh[6:5]): VGH voltage level selection

| D6 | <b>D</b> 5 | VGH Voltage         |

|----|------------|---------------------|

| 0  | 0          | VGL  + 2V.          |

| 0  | 1          | VGL  + 3V.          |

| 1  | 0          | VGL  + 4V.          |

| 1  | 1          | VGL + 5V. (default) |

| Dogletor |                 | Parameter Data |                    |    |    |    |                   |    |  |  |  |  |

|----------|-----------------|----------------|--------------------|----|----|----|-------------------|----|--|--|--|--|

| Register | D7              | D6             | D5                 | D4 | D3 | D2 | D1                | D0 |  |  |  |  |

| R3Ch     | GAMMA_EN<br>(0) |                | L127P_SEL<br>(011) |    | Х  | L  | 000P_SEL<br>(100) |    |  |  |  |  |

GAMMA\_EN: Gamma Reference Point Control Enable

| D7 | GAMMA_EN Function                                      |

|----|--------------------------------------------------------|

| 0  | VN reference point control setting follow VP (default) |

| 1  | VP / VN Reference point control independently          |

L127P\_SEL: Gamma op output selection to level VP127; L000P\_SEL: Gamma op output selection to level VP000;

| Reference point | 000  | 001  | 010  | 011     | 100     | 101  | 110  | 111  |

|-----------------|------|------|------|---------|---------|------|------|------|

| L000P(100)      | -4△V | -3∆V | -2△V | -1△V    | Default | +1△V | +2△V | +3△V |

| L127P(011)      | -3△V | -2△V | -1△V | Default | +1△V    | +2△V | +3△V | +4△V |

Note:(1) For Low Voltage LC application, △V= 25mV ∘

(2) For Normal Voltage LC application, △V= 40mV ∘

| Register |    |    |                    | Param | eter Data |                    |                   |    |  |

|----------|----|----|--------------------|-------|-----------|--------------------|-------------------|----|--|

| negister | D7 | D6 | D5                 | D4    | D3        | D2                 | D1                | D0 |  |

| R3Dh     | Х  |    | L127N_SEI<br>(011) | -     | Х         | L                  | 000N_SEL<br>(111) |    |  |

| R3Eh     | Х  |    | L016N_SEI<br>(101) | -     | Х         | L008N_SEL<br>(100) |                   |    |  |

| R3Fh     | Х  |    | L050N_SEI<br>(101) | -     | Х         | L032N_SEL<br>(100) |                   |    |  |

| R40h     | Х  |    | L096N_SEI<br>(100) | -     | X         | L072N_SEL<br>(011) |                   |    |  |

| R41h     | Х  |    | L120N_SEI<br>(101) | -     | Х         | L110N_SEL<br>(100) |                   |    |  |

L127N\_SEL: Gamma op output selection to level VN127;

L000N\_SEL: Gamma op output selection to level VN000;

L016N SEL: Gamma op output selection to level VN16;

L008N\_SEL: Gamma op output selection to level VN8;

L050N\_SEL: Gamma op output selection to level VN50;

L032N SEL: Gamma op output selection to level VN32;

L096N\_SEL: Gamma op output selection to level VN96;

L072N\_SEL: Gamma op output selection to level VN72; L120N\_SEL: Gamma op output selection to level VN120; L110N\_SEL: Gamma op output selection to level VN110;

| Reference point | 000  | 001  | 010  | 011     | 100     | 101     | 110  | 111     |

|-----------------|------|------|------|---------|---------|---------|------|---------|

| L000N(000)      | +7△V | +6△V | +5△V | +4△V    | +3△V    | +2△V    | +1△V | Default |

| L008N(100)      | -4△V | -3△V | -2△V | -△V     | Default | +△V     | +2△V | +3△V    |

| L016N(101)      | -5∆V | -4△V | -3△V | -2△V    | -△V     | Default | +△V  | +2△V    |

| L032N(100)      | -4△V | -3△V | -2△V | -△V     | Default | +△V     | +2△V | +3△V    |

| L050N(101)      | -5∆V | -4△V | -3△V | -2△V    | -△V     | Default | +△V  | +2∆V    |

| L072N(011)      | -3△V | -2△V | -△V  | Default | +△V     | +2△V    | +3△V | +4△V    |

| L096N(100)      | -4△V | -3△V | -2△V | -△V     | Default | +△V     | +2△V | +3△V    |

| L110N(100)      | -4△V | -3∆V | -2△V | -△V     | Default | +△V     | +2△V | +3△V    |

| L120N(101)      | -5∆V | -4△V | -3△V | -2△V    | -△V     | Default | +△V  | +2△V    |

Note:(1) For Low Voltage LC application, △V= 25mV ∘

(2) For Normal Voltage LC application, △V= 40mV ∘

| Register |    |                |                | Parame | eter Data |    |    |    |

|----------|----|----------------|----------------|--------|-----------|----|----|----|

|          | D7 | D6             | D5             | D4     | D3        | D2 | D1 | D0 |

| R55h     | х  | INV_SEL<br>(0) | DAT_INV<br>(0) | х      | х         | х  | х  | х  |

### DAT\_INV (R55h[5]): Source output Inversion control

| D5 | DAT_INV Function              |

|----|-------------------------------|

| 0  | Data output normal. (default) |

| 1  | Data output inversion.        |

### INV\_SEL (R55h[6]): Inversion selection

| I | D6 | INV_SEL Function              |

|---|----|-------------------------------|

| I | 0  | One line inversion. (default) |

| I | 1  | Column inversion.             |

| Register |                 | Parameter Data |    |    |    |    |    |    |  |  |  |  |

|----------|-----------------|----------------|----|----|----|----|----|----|--|--|--|--|

|          | D7              | D6             | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |  |

| R57h     | VGHL_ENB<br>(0) | х              | х  | х  | х  | х  | х  | х  |  |  |  |  |

### VGHL\_ENB (R57h[7]): VGH/VGL charge pump control

| D7 | VGHL_ENB Function                                             |

|----|---------------------------------------------------------------|

| 0  | VGH/VGL charge pump enable. ( <b>default</b> )                |

| 1  | VGH/VGL charge pump enable, for external VGH/VGL application. |

<sup>\*</sup>Note: don't apply external power to VGH and VGL pad when VGHL\_EN=0 and VGHL\_ENB=0.

### TM027CDH08 V1.0

| Pogletor |    |    |    | Parameter Data |    |    |            |           |  |  |  |  |  |  |  |

|----------|----|----|----|----------------|----|----|------------|-----------|--|--|--|--|--|--|--|

| Register | D7 | D6 | D5 | D4             | D3 | D2 | D1         | D0        |  |  |  |  |  |  |  |

| R5Ah     | х  | х  | х  | х              | х  | х  | VGL_<br>(1 | SEL<br>0) |  |  |  |  |  |  |  |

### VGL\_SEL (R5Ah[1:0]): VGL voltage level selection

| D1 | D0 | VGL Voltage    |

|----|----|----------------|

| 0  | 0  | -8V            |

| 0  | 1  | -9V            |

| 1  | 0  | -10V (default) |

| 1  | 1  | -11V           |

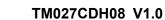

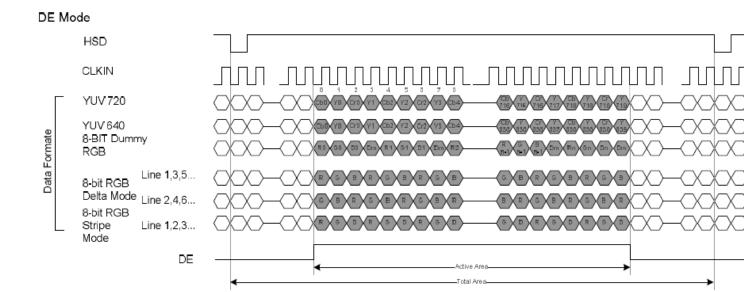

### 5.4 DATA INPUT FORMAT

### Serial 8-bit RGB / 8-bit Dummy RGB / YUV Mode Data format

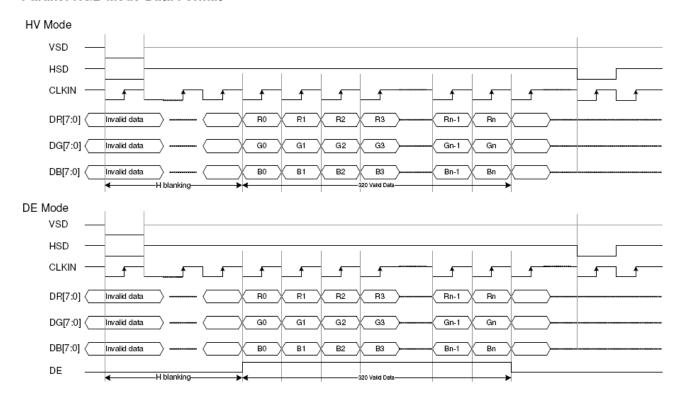

### Parallel RGB Mode Data Format

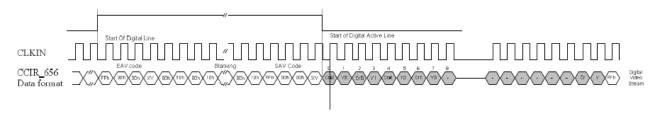

### CCIR\_656 Mode Data format

- FF 00 00 XY signals are involoved with HSD, VSD and Field.

- XY encode following bits:

F = field select

V = indicate vertical blanking

H = 1, if EAV else 0 for SAV

P3-P0 = protection bits:

$P3 = V \oplus H P2 = F \oplus H P1 = F \oplus V P0 = F \oplus V \oplus H \oplus :$ Represents the exclusive-OR function.

|                              | XY                  |  |  |  |  |  |    |  |  |

|------------------------------|---------------------|--|--|--|--|--|----|--|--|

| D7(MSB) D6 D5 D4 D3 D2 D1 D0 |                     |  |  |  |  |  | D0 |  |  |

| 1                            | 1 F V H P3 P2 P1 P0 |  |  |  |  |  |    |  |  |

- Control is provided through "End of Video" (EAV) and "Start of Video" (SAV) timing references.

- Horizontal blanking section cosists of repeating pattern 80 10 80 10

### TM027CDH08 V1.0

### Data Active Area

| Input Format | Format Standard | CLKIN(MHz)     | Н | Total AREA | Active AREA |  |

|--------------|-----------------|----------------|---|------------|-------------|--|

|              | CCIR_601        | fCLKIN = 27    | 1 | 1716       | 1440        |  |

| YUV          | CCIR_656        | ICLNIN = 27    | 1 | 1728       |             |  |

|              | CCIR_601        | fCLKIN = 24.54 | 1 | 1560       | 1280        |  |

| 8-bit Dummy  | NTSC/PAL        | fCLKIN = 27    | 4 | 1560       | 1440        |  |

| RGB          | NISOFAL         | fCLKIN = 24.54 |   | 1560       | 1280        |  |

| 8-bit RGB    | NTSC            | fCLKIN = 27    | 1 | 1716       | 960         |  |

| 24bit RGB    | 320RGB x 240    | fCLKIN =6.4    | 1 | 390        | 320 (RGB)   |  |

|              |                 |                |   |            |             |  |

(Unit:CLKIN)

### CCIR656/YUV640/YUV720 to RGB Conversion Formula

$R_n = 1.164^* [(Y_{2n\text{-}1} + Y_{2n})/2 \text{-} 16] + 1.596^* (Cr_n\text{-} 128)$

$G_n = 1.164^*[(Y_{2n\text{-}1}\text{-}1+Y_{2n})/2\text{-}16] - 0.813^*(Cr_n\text{-}128) - 0.392^*(Cb_n\text{-}128)$

$B_n = 1.164^*[(Y_{2n-1}+Y_{2n})/2-16] + 2.017^*(Cb_{n-128})$

Where Y: 16~235 Cr: 16~240 Cb: 16~240

### 5.5 INPUT TIMING FORMAT

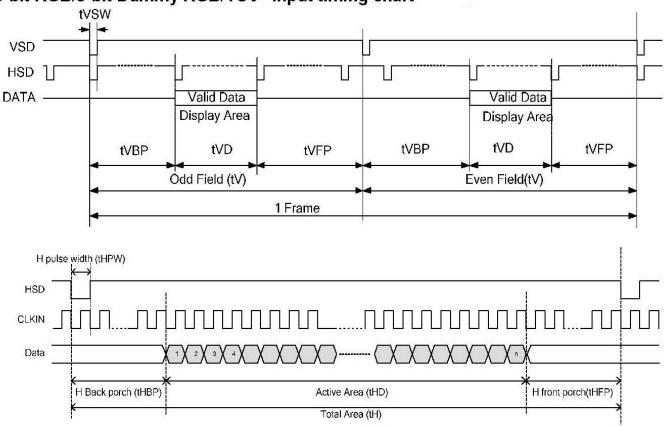

### 8-bit RGB/8-bit Dummy RGB/YUV Input timing chart

# 8-bit RGB input timing

| Parameter       |                 | Cumbal |         | Interlace |        | Unit  |

|-----------------|-----------------|--------|---------|-----------|--------|-------|

| raiailletei     |                 | Symbol | Min.    | Тур.      | Max.   | OIIIL |

| CLKIN frequ     | iency           | fCLKIN | 13.5    | 27        | 27.19  | MHz   |

| HSD period      |                 | tH     | 1024    | 1716      | 1728   | CLKIN |

| HSD display     | period          | tHD    |         | 960       |        | CLKIN |

| HSD back p      | orch            | tHBP   | 50      | 70        | 255    | CLKIN |

| HSD front p     | orch            | tHFP   | 14      | 686       | 718    | CLKIN |

| HSD pulse width |                 | tHSW   | 1       | 1         | tHBP-1 | CLKIN |

| VSD period      | time            | tV     | 242.5   | 262.5     | 450.5  | Н     |

| Vertical disp   | lay area        | tVD    |         | 240       |        | Н     |

| VSD             | Odd field       | tVBP   | 3       | 21        | 31     | Н     |

| back porch      | Even field      | LVDP   | 3.5     | 21.5      | 31.5   | П     |

| VSD             | Odd field       | A/CD   | 1.5     | 1.5       | 179.5  | 111   |

| front porch     | Even field      | tVFP   | 1       | 1         | 179    | Н     |

| VSD pulse v     | VSD pulse width |        | 1 CLKIN | 1CLKIN    | 6H     |       |

| 1 Frame         |                 |        | 485     | 525       | 901    | Н     |

### 8-bit Dummy RGB input timing

8-bit Dummy RGB (320 mode/NTSC/24.535Mhz) input timing

|               |                 | 1 1    |       | lusta ula a a |          | 1      |

|---------------|-----------------|--------|-------|---------------|----------|--------|

| Parameter     |                 | Symbol |       | Interlace     | <u> </u> | Unit   |

| 1 drameter    |                 | Oyboi  | Min.  | Тур.          | Max.     | O III. |

| CLKIN frequ   | iency           | fCLKIN | 20.45 | 24.535        | 30       | MHz    |

| HSD period    |                 | tH     | 1306  | 1560          | 1907     | CLKIN  |

| HSD display   | period          | tHD    |       | 1280          |          | CLKIN  |

| HSD back p    |                 | tHBP   | 3     | 241           | 255      | CLKIN  |

| HSD front p   | HSD front porch |        | 25    | 39            | 372      | CLKIN  |

| HSD pulse     | width           | tHSW   | 1     | 1             | 200      | CLKIN  |

| VSD period    | time            | tV     | 242.5 | 262.5         | 450.5    | H      |

| Vertical disp | lay area        | tVD    | 240   |               |          | Н      |

| VSD           | Odd field       | tVBP   | 3     | 21            | 31       | 11     |

| back porch    | Even field      | T LABE | 3.5   | 21.5          | 31.5     | Н      |

| VSD           | Odd field       | tVFP   | 1.5   | 1.5           | 179.5    | Lii    |

| front porch   | Even field      | TIVEE  | 1     | 1             | 179      | Н Н    |

| VSD pulse v   | VSD pulse width |        | 1     | 1             | 200      | CLKIN  |

| 1 Frame       | ·               |        | 485   | 525           | 901      | Н      |

8-bit Dummy RGB (320 mode/PAL/24.375Mhz) input timing

| Parameter       |             | Symbol   |       | Interlace |       | Unit  |

|-----------------|-------------|----------|-------|-----------|-------|-------|

| Parameter       | raiailletei |          | Min.  | Тур.      | Max.  | Onit  |

| CLKIN frequ     | lency       | fCLKIN   | 20.45 | 24.375    | 30    | MHz   |

| HSD period      |             | tH       | 1306  | 1560      | 1920  | CLKIN |

| HSD display     | period      | tHD      |       | 1280      |       | CLKIN |

| HSD back p      | orch        | tHBP     | 3     | 241       | 255   | CLKIN |

| HSD front porch |             | tHFP     | 25    | 39        | 385   | CLKIN |

| HSD pulse width |             | tHSW     | 1     | 1         | 200   | CLKIN |

| VSD period      | time        | tV       | 292.5 | 312.5     | 450.5 | Н     |

| Vertical disp   | lay area    | tVD      | 288   |           |       | Н     |

| VSD             | Odd field   | tVBP     | 3     | 23        | 34    | 11    |

| back porch      | Even field  | J MADE [ | 3.5   | 23.5      | 34.5  | - H   |

| VSD             | Odd field   | W/ED     | 1.5   | 1.5       | 128.5 | 10    |

| front porch     | Even field  | tVFP     | 1     | 1         | 128   | 1 H   |

| VSD pulse v     | width       | tVSW     | 1     | 1         | 200   | CLKIN |

| 1 Frame         |             |          | 585   | 625       | 901   | Н     |

8-bit Dummy RGB (360 mode/NTSC/27Mhz) input timing

| Parameter              |            | Cump had |       | Interlace |       | Limit |

|------------------------|------------|----------|-------|-----------|-------|-------|

| raiametei              |            | Symbol   | Min.  | Тур.      | Max.  | Unit  |

| CLKIN frequ            | uency      | fCLKIN   | 23    | 27        | 30    | MHz   |

| HSD period             |            | tH       | 1466  | 1716      | 1907  | CLKIN |

| HSD display            | period     | tHD      |       | 1440      |       | CLKIN |

| HSD back p             |            | tHBP     | 3     | 241       | 255   | CLKIN |

| HSD front porch        |            | tHFP     | 25    | 35        | 212   | CLKIN |

| HSD pulse width        |            | tHSW     | 1     | 1         | 200   | CLKIN |

| VSD period             | time       | tV       | 242.5 | 262.5     | 450.5 | Н     |

| Vertical disp          | olay area  | tVD      | 240   |           |       | Н     |

| VSD                    | Odd field  | 1 VDD    | 3     | 21        | 31    |       |

| back porch             | Even field | tVBP     | 3.5   | 21.5      | 31.5  | H     |

| VSD                    | Odd field  | N/ED     | 1.5   | 1.5       | 179.5 | 1.7   |

| front porch Even field |            | tVFP     | 1     | 1         | 179   | H     |

| VSD pulse width        |            | tVSW     | 1     | 1         | 200   | CLKIN |

| 1 Frame                |            |          | 485   | 525       | 901   | Н     |

### TM027CDH08 V1.0

8-bit Dummy RGB (360 mode/PAL/27Mhz) input timing

| Parameter              |                 | Symbol  |       | Interlace |       | Unit  |

|------------------------|-----------------|---------|-------|-----------|-------|-------|

| raiailletei            |                 | Symbol  | Min.  | Тур.      | Max.  | John  |

| CLKIN frequ            | iency           | fCLKIN  | 23    | 27        | 30    | MHz   |

| HSD period             |                 | tH      | 1466  | 1728      | 1920  | CLKIN |

| HSD display            | period          | tHD     |       | 1440      |       | CLKIN |

| HSD back p             | orch            | tHBP    | 3     | 241       | 255   | CLKIN |

| HSD front p            | HSD front porch |         | 25    | 47        | 225   | CLKIN |

| HSD pulse v            | width           | tHSW    | 1     | 1         | 200   | CLKIN |

| VSD period             | time            | tV      | 292.5 | 312.5     | 450.5 | Н     |

| Vertical disp          | lay area        | tVD     |       | 288       |       |       |

| VSD                    | Odd field       | tVBP    | 3     | 23        | 34    | Н     |

| back porch             | Even field      | J MAD I | 3.5   | 23.5      | 34.5  |       |

| VSD                    | Odd field       | tVFP    | 1.5   | 1.5       | 128.5 | 1.1   |

| Front porch Even field |                 |         | 1     | 1         | 128   | H     |

| VSD pulse v            | VSD pulse width |         | 1     | 1         | 200   | CLKIN |

| 1 Frame                |                 |         | 585   | 625       | 901   | Н     |

YUV720 and YUV640 input timing YUV 720 mode/NTSC input timing

| Parameter              |                 | Symbol   |            | Interlace |                 | 1144  |

|------------------------|-----------------|----------|------------|-----------|-----------------|-------|

| Parameter              | raiametei       |          | Min.       | Тур.      | Max.            | Unit  |

| CLKIN frequ            | uency           | fCLKIN   | 153        | 27        | =               | MHz   |

| HSD period             |                 | tH       |            | 1716      | <u>14</u><br>20 | CLKIN |

| HSD display            | / period        | tHD      |            | 1440      |                 | CLKIN |

| HSD back p             | orch            | tHBP     | #1         | 240       | -               | CLKIN |

| HSD front p            | HSD front porch |          | -          | 36        | -               | CLKIN |

| HSD pulse              | HSD pulse width |          | -          | 1         |                 | CLKIN |

| VSD period             | time            | tV       | -          | 262.5     | -               | Н     |

| Vertical disp          | lay area        | tVD      | 240        |           |                 | Н     |

| VSD                    | Odd field       | tVBP     | 3          | 21        | <u>a</u> 1      | 1.1   |

| back porch             | Even field      | J LABA L | 29         | 21.5      | 40              | H     |

| VSD                    | Odd field       | #\/ED    | 48         | 1.5       | -               | 111   |

| front porch Even field |                 | tVFP     | <b>H</b> 1 | 1         | -               | H     |

| VSD pulse width        |                 | tVSW     | -          | 1         | 8               | CLKIN |

| 1 Frame                |                 |          |            | 525       | -               | Н     |

YUV 720 mode/PAL input timing

| Parameter       |             | Symbol |             | Interlace |      | Unit  |

|-----------------|-------------|--------|-------------|-----------|------|-------|

| Parameter       | raiailletei |        | Min.        | Тур.      | Max. | Unit  |

| CLKIN frequ     | iency       | fCLKIN | <b></b>     | 27        | =    | MHz   |

| HSD period      |             | tH     | - 8         | 1728      | 9    | CLKIN |

| HSD display     | period      | tHD    |             | 1440      |      | CLKIN |

| HSD back p      | orch        | tHBP   | = 1         | 240       | =    | CLKIN |

| HSD front porch |             | tHFP   | <b>*</b>    | 48        |      | CLKIN |

| HSD pulse width |             | tHSW   | -           | 1         | 8    | CLKIN |

| VSD period      | time        | tV     | -           | 312.5     | -    | Н     |

| Vertical disp   | olay area   | tVD    | 288         |           |      | H     |

| VSD             | Odd field   | W/DD   | - 8         | 24        | 9    | 10    |

| back porch      | Even field  | tVBP   | 40          | 24.5      | #    | Н     |

| VSD             | Odd field   | tVFP   | 48          | 0.5       | =    | 111   |

| front porch     | Even field  |        | <b>±</b> (  | 0         | H    | H     |

| VSD pulse width |             | tVSW   | -           | 1         | -    | CLKIN |

| 1 Frame         |             |        | <b>=</b> 10 | 625       | - 5  | Н     |

### TM027CDH08 V1.0

YUV 640 mode/NTSC input timing

| Parameter              |                 | Symbol   |          | Interlace |          | Unit  |

|------------------------|-----------------|----------|----------|-----------|----------|-------|

| Parameter              |                 | Syllibol | Min.     | Тур.      | Max.     | OIIIL |

| CLKIN frequ            | iency           | fCLKIN   | -        | 24.535    |          | MHz   |

| HSD period             |                 | tH       | -        | 1560      | -        | CLKIN |

| HSD display            | / period        | tHD      |          | 1280      |          | CLKIN |

| HSD back p             | orch            | tHBP     | <u>u</u> | 240       |          | CLKIN |

| HSD front p            | orch            | tHFP     | -        | 40        | 2        | CLKIN |

| HSD pulse v            | HSD pulse width |          | <u> </u> | 1         | =        | CLKIN |

| VSD period             | time            | tV       | -        | 262.5     | 4        | Н     |

| Vertical disp          | olay area       | tVD      | 240      |           |          | H     |

| VSD                    | Odd field       | tVBP     | -        | 21        | -        | Н     |

| back porch             | Even field      | ] IVEF [ | <u>=</u> | 21.5      | 2        |       |

| VSD                    | Odd field       | tVFP     | <u> </u> | 1.5       | <u> </u> | 11    |

| front porch Even field |                 |          | =        | 1         | _        | H     |

| VSD pulse v            | VSD pulse width |          | -        | 1         | =        | CLKIN |

| 1 Frame                |                 |          | -        | 525       | -        | Н     |

YUV 640 mode/PAL input timing

| Parameter       |            | Symbol   |      | Interlace |             | Unit    |  |

|-----------------|------------|----------|------|-----------|-------------|---------|--|

| raiailletei     |            | Syllibol | Min. | Тур.      | Max.        | - Ollit |  |

| CLKIN frequ     | iency      | fCLKIN   | -    | 24.375    | -           | MHz     |  |

| HSD period      |            | tH       | 7.0  | 1560      |             | CLKIN   |  |

| HSD display     | period     | tHD      |      | 1280      |             | CLKIN   |  |

| HSD back p      | orch       | tHBP     | 4    | 240       | =           | CLKIN   |  |

| HSD front porch |            | tHFP     | -    | 40        | -           | CLKIN   |  |

| HSD pulse width |            | tHSW     | ÷    | 1         | =           | CLKIN   |  |

| VSD period      | time       | tV       | +    | 312.5     | ÷           | H       |  |

| Vertical disp   | lay area   | tVD      |      | 288       |             | Н       |  |

| VSD             | Odd field  | tVBP     | 5    | 24        | -           | 13      |  |

| back porch      | Even field | J MADE [ |      | 24.5      |             | - H     |  |

| VSD             | Odd field  | AVED.    | 4    | 0.5       | <u>10</u> 4 | 17      |  |

| front porch     | Even field | tVFP     | =    | 0         | 2           | -  H    |  |

| VSD pulse width |            | tVSW     | -    | 1         | =           | CLKIN   |  |

| 1 Frame         |            |          | -    | 625       | -           | Н       |  |

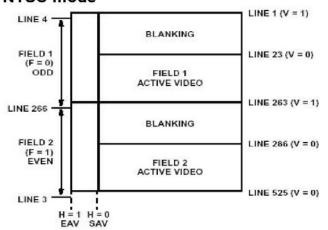

# CCIR656 input timing NTSC mode

| LINE<br>NUMBER | F | v  | H<br>(EAV) | H<br>(SAV) |

|----------------|---|----|------------|------------|

| 1-3            | 1 | 1  | 1          | 0          |

| 4-22           | 0 | 1. | 1          | 0          |

| 23-262         | 0 | 0  | -1         | 0          |

| 263-265        | 0 | 1  | 1          | -0         |

| 266-285        | 1 | 1  | 1          | 0          |

| 286-525        | 1 | 0  | 1          | 0          |

|   | F          | Ή   | ٧               |

|---|------------|-----|-----------------|

| 1 | EVEN Field | EAV | BLANKING        |

| 0 | ODD Field  | SAV | ACTIVE<br>VIDEO |

### PAL mode

|   | F          | H   | ٧               |

|---|------------|-----|-----------------|

| 1 | EVEN Field | EAV | BLANKING        |

| 0 | ODD Field  | SAV | ACTIVE<br>VIDEO |

| LINE<br>NUMBER | F   | v  | H<br>(EAV) | H<br>(SAV) |

|----------------|-----|----|------------|------------|

| 1-22           | 0   | 1  | 1          | 0          |

| 23-310         | 0   | 0  | 1          | 0          |

| 311-312        | 0   | 1  | 1          | 0          |

| 313-335        | 1   | .1 | 1          | 0          |

| 336-623        | 1   | 0  | 1          | 0          |

| 624-625        | -1. | 1  | 1          | 0          |

TM027CDH08 V1.0

### 5.6 AC ELECTRICAL CHARACTERISTICS

(VDD=3.0~3.6V, VDDIO=AVDD=VDD, AGND=GND=0V, TA=25°C)

| Parameter                           | Symbol   | Min. | Тур.  | Max. | Unit  | Conditions                                                      |

|-------------------------------------|----------|------|-------|------|-------|-----------------------------------------------------------------|

| HSD period time                     | Th       | 60   | 63.56 | 67   | us    |                                                                 |

| VSD setup time                      | Tvst     | 12   | -     | -    | ns    |                                                                 |

| VSD hold time                       | Tvhd     | 12   | 4     | -    | ns    |                                                                 |

| HSD setup time                      | Thst     | 12   | -     | -    | ns    |                                                                 |

| HSD hold time                       | Thhd     | 12   | -     | -    | ns    |                                                                 |

| Data setup time                     | Tdsu     | 12   | -     | -    | ns    | DB0~DB7 to                                                      |

| Data hold time                      | Tdhd     | 12   | -     |      | ns    | DB0~DB7 to                                                      |

| Time that VSD to 1st Gate output    | Tstv     | 0    | 21    | 31   | Н     | @ 8-bit RGB, 8-bit Dummy RGB<br>NTSC, Delay by<br>VBLK setting. |

| Time that CCIR_V to 1st Gate output | Tstv     | 0    | 22    | 31   | Н     | @ CCIR656 NTSC,<br>Delay by VBLK setting.                       |

| Time that CCIR_V to 1st Gate output | Tstv     | 3    | 24    | 34   | Н     | @ 8-bit Dummy RGB & CCIR656<br>PAL,<br>Delay by VBLK setting.   |

| Source output setting time (*1)     | Tst      | =    | -     | 8    | us    | R= <mark>25K ohm</mark> , C= 30 pF<br>10% → 90% final.          |

| Gate output setting time (*1)       | Tstg     | 1    | 0.5   | 1    | us    | R= 3K ohm , C= 25 pF<br>10% → 90% final.                        |

| VCOM setting time (*1)              | Tst,vcom |      | -     | 9    | us    | R= 200 ohm , C= 5 nF<br>10% → 90% final.                        |

| Time that HSD width                 | Twh      | 1    | -     | -    | CLKIN |                                                                 |

### Ps. (\*1) Test Condition:

When the tested signal is changed from Vo, min to Vo, max, the time that is from the start of change to the time that the swing voltage at point B is less than +/- 20 mV is called the setting time of the tested signal.

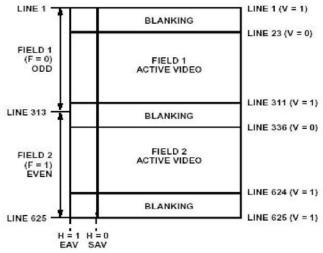

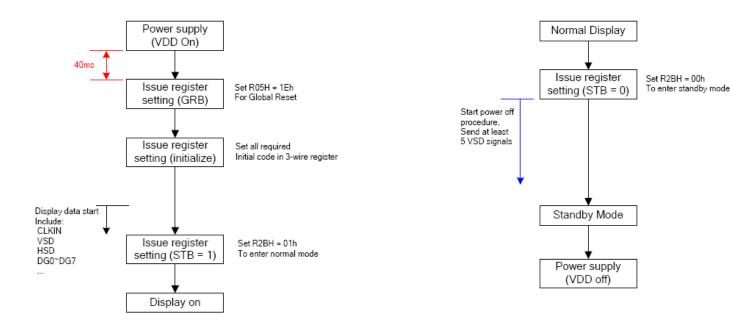

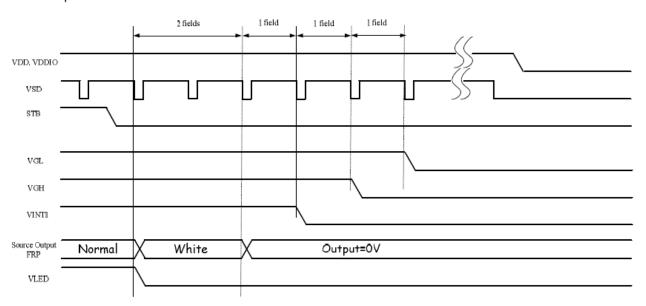

# 6 Power On/Off Sequence

### 6.1 INITIALIZE FLOW CHART

### 6.2 POWER ON SEQUENCE

Note: 1. The RSTB should keep low until VDDIO was stable, and set to high before SPI command start 2. After STB set to 1, it takes 9 VSD pulse for power on operation

Power Off Sequence

## Optical Characteristics

### 7.1 Optical Specification

Ta=25°C

| Item            |           | Symbol | Condition          | Min   | Тур   | Max   | Unit              | Remark          |

|-----------------|-----------|--------|--------------------|-------|-------|-------|-------------------|-----------------|

| View Angles     |           | θТ     | CR≧10              | 50    | 60    | -     | Dograd            | Nata O          |

|                 |           | θВ     |                    | 60    | 70    | -     |                   |                 |

| View Angles     |           | θL     | OIX≦ IU            | 60    | 70    | -     | Degree            | Note 2          |

|                 |           | θR     |                    | 60    | 70    | -     |                   |                 |

| Contrast Ratio  | )         | CR     | θ=()°              | 400   | 500   | ı     | Note1<br>Note3    |                 |

| Response Tim    | 10        | Ton    | 25℃                |       | 30    | 45    | ms                | Note1           |

| iveshouse tiili | ie –      | Toff   | 25 (               | _     | 30    | 40    | 1115              | Note4           |

|                 | White x y |        | 0.251              | 0.301 | 0.351 |       |                   |                 |

|                 |           | у      | Backlight is<br>on | 0.280 | 0.330 | 0.380 | - 1               | Note5,<br>Note1 |

|                 | Red       | х      |                    | 0.546 | 0.596 | 0.646 |                   |                 |

| Chromaticity    |           | у      |                    | 0.293 | 0.343 | 0.393 |                   |                 |

| Chilomaticity   | Green     | х      |                    | 0.293 | 0.343 | 0.393 |                   |                 |

|                 |           | у      |                    | 0.483 | 0.533 | 0.583 |                   |                 |

|                 |           | х      |                    | 0.098 | 0.148 | 0.198 |                   |                 |

|                 | Diue      | Blue   |                    | 0.069 | 0.119 | 0.169 |                   |                 |

| Uniformity      |           | U      | -                  | 75    | 80    | -     | %                 | Note1<br>Note6  |

| NTSC            |           | -      | -                  | -     | 40    | -     | %                 | Note 5          |

| Luminance       |           | L      | -                  | 220   | 270   | -     | cd/m <sup>2</sup> | Note1<br>Note7  |

### **Test Conditions:**

- 1.  $V_F$ =3.2V,  $I_F$ =25mA (Backlight Current), the ambient temperature is 25  $^{\circ}$ C.

- 2. The test systems refer to Note 1 and Note 2.

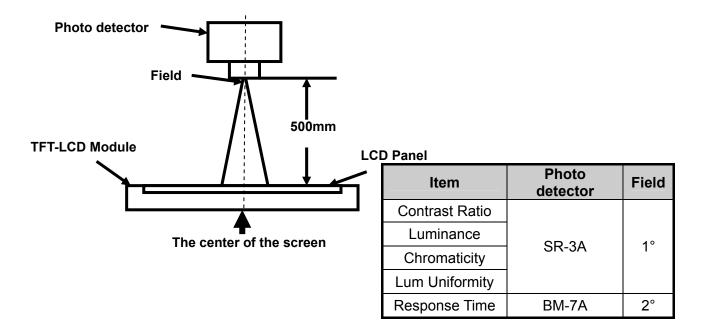

Note 1: Definition of optical measurement system.

The optical characteristics should be measured in dark room. After 5 minutes operation, the optical properties are measured at the center point of the LCD screen. All input terminals LCD panel must be ground when measuring the center area of the panel.

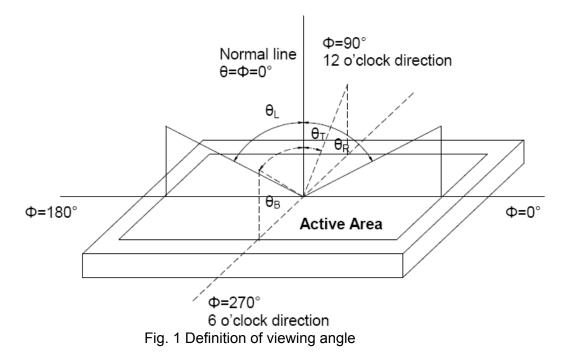

Note 2: Definition of viewing angle range and measurement system.

viewing angle is measured at the center point of the LCD by CONOSCOPE(ergo-80).

The information contained herein is the exclusive property of SHANGHAI TIANMA MICRO-ELECTRONICS Corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of SHANGHAI TIANMA MICRO-ELECTRONICS Corporation.

Note 3: Definition of contrast ratio

Contrast ratio (CR) = Luminance measured when LCD is on the "White" state

Luminance measured when LCD is on the "Black" state

"White state ": The state is that the LCD should driven by Vwhite.

"Black state": The state is that the LCD should driven by Vblack.

Vwhite: To be determined Vblack: To be determined.

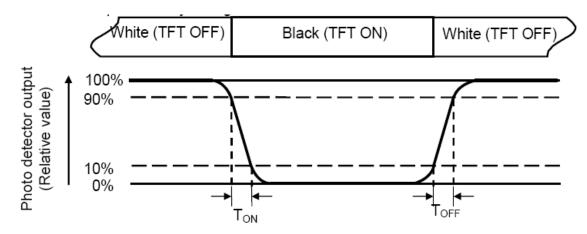

### Note 4: Definition of Response time

The response time is defined as the LCD optical switching time interval between "White" state and "Black" state. Rise time (TON) is the time between photo detector output intensity changed from 90% to 10%. And fall time (TOFF) is the time between photo detector output intensity changed from 10% to 90%.

Note 5: Definition of color chromaticity (CIE1931)

Color coordinates measured at center point of LCD.

### Note 6: Definition of Luminance Uniformity

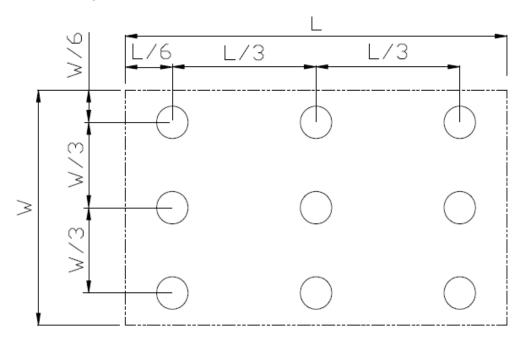

Active area is divided into 9 measuring areas (Refer Fig. 2). Every measuring point is placed at the center of each measuring area.

Luminance Uniformity(U) = Lmin / Lmax

L----- Active area length W----- Active area width

Fig. 2 Definition of uniformity

Lmax: The measured maximum luminance of all measurement position.

Lmin: The measured minimum luminance of all measurement position.

### Note 7: Definition of Luminance:

Measure the luminance of white state at center point.

# 8 Environmental / Reliability Tests