TD025WHEB2

# Preliminary

Ver.: 0.01

# **LTPS LCD Specification**

# Model Name: TD025WHEB2

| Customer Signature |  |

|--------------------|--|

|                    |  |

|                    |  |

| Date               |  |

|                    |  |

This technical specification is subjected to change without notice

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

# **Table of Contents**

| NO. | Item                       | Page |

|-----|----------------------------|------|

|     | Cover Sheet                | 1    |

|     | Table of Contents          | 2    |

|     | Record of Revision         | 3    |

| 1   | Features                   | 4    |

| 2   | General Specifications     | 4    |

| 3   | Input / Output Terminals   | 5    |

| 4   | Absolute Maximum Ratings   | 7    |

| 5   | Electrical Characteristics | 8    |

| 6   | Timing Chart               | 9    |

| 7   | Optical Characteristics    | 18   |

| 8   | Reliability                | 21   |

| 9   | Handling Cautions          | 22   |

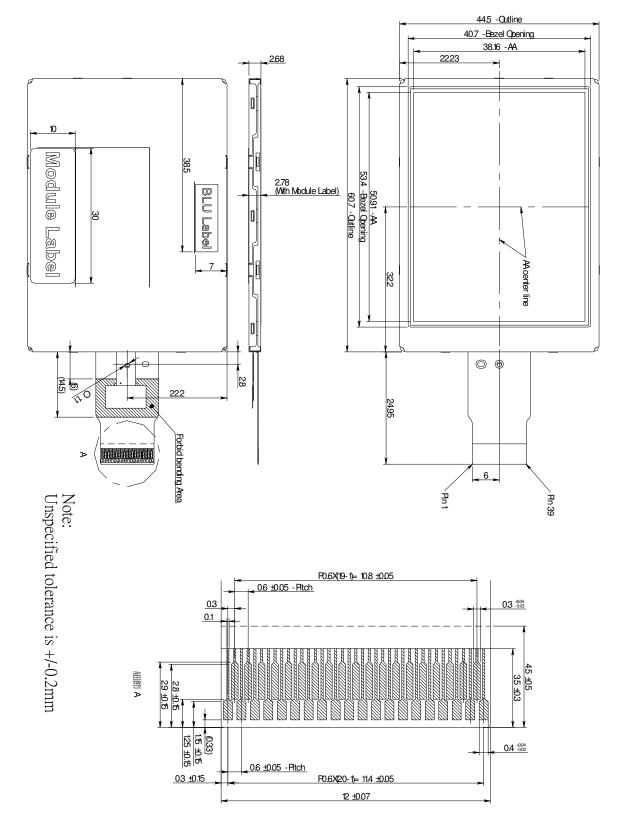

| 10  | Mechanical Drawing         | 23   |

| 11  | Packing Drawing            | 24   |

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

# TD025WHEB2

#### **Record of Revision**

| Rev  | Issue Date    | Description                                                |

|------|---------------|------------------------------------------------------------|

| 0.00 | Nov 06, 2004  | New create.                                                |

| 0.10 | June. 8, 2005 | Page 4: Modify feature description                         |

|      |               | Page 6: Add Note 3-1                                       |

|      |               | Page 9: Modify "6. timing chart"                           |

|      |               | Page16: Optical characteristics: update max. or min. value |

|      |               | Page21: Add "11. packing drawing"                          |

|      |               |                                                            |

|      |               |                                                            |

|      |               |                                                            |

|      |               |                                                            |

|      |               |                                                            |

|      |               |                                                            |

|      |               |                                                            |

|      |               |                                                            |

|      |               |                                                            |

|      |               |                                                            |

|      |               |                                                            |

|      |               |                                                            |

|      |               |                                                            |

|      |               |                                                            |

|      |               |                                                            |

|      |               |                                                            |

|      |               |                                                            |

|      |               |                                                            |

|      |               |                                                            |

|      |               |                                                            |

|      |               |                                                            |

|      |               |                                                            |

|      |               |                                                            |

|      |               |                                                            |

|      |               |                                                            |

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

# 1. FEATURES

The 2.5" LCD module is the active matrix color TFT LCD module. LTPS (Low Temperature Poly Silicon) TFT technology is applied with vertical and horizontal drivers built on the panel. Both of horizontal and vertical scan are reversible and controlled by the serial interface commands. The product is designed for the requirement of the green product, and the specification complies with Toppoly's "Green Product Chemical Substance Specification Standard Hand Book".

# 2. GENERAL SPECIFICATIONS

| Item                      | Description               | Unit |

|---------------------------|---------------------------|------|

| Display Size (Diagonal)   | 2.5                       | Inch |

| Display Type              | Transmissive              | -    |

| Active Area (HxV)         | 50.91 x 38.16             | mm   |

| Number of Dots (HxV)      | 960 x 240                 | Dot  |

| Dot Pitch (HxV)           | 0.053x0.159               | mm   |

| Color Arrangement         | RGB Delta                 | -    |

| Color Numbers             | 16Million                 | -    |

| Outline Dimension (HxVxT) | 60.7x44.5x2.68*(Approach) | mm   |

| Weight                    | 14.5                      | G    |

| Panel surface treatment   | Hard Coating (3H)         | -    |

\*Exclude FPC and protrusions.

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

### 3. INPUT/OUTPUT TERMINALS

3.1 TFT LCD Panel

Recommend connector:

# Compatible with JAE IL-FHJ-39S-HF-A1

| Pin | Symbol | I/O | Description                                                   | Remark   |

|-----|--------|-----|---------------------------------------------------------------|----------|

| 1   | CP3    | С   | Capacitor for charge pump                                     |          |

| 2   | CP4    | С   | Capacitor for charge pump                                     |          |

| 3   | CP5    | С   | Capacitor for charge pump                                     |          |

| 4   | CP6    | С   | Capacitor for charge pump                                     |          |

| 5   | CP7    | С   | Capacitor for charge pump                                     |          |

| 6   | CP8    | С   | Capacitor for charge pump                                     |          |

| 7   | NC     |     | No connection                                                 |          |

| 8   | PCDL   | С   | Capacitor for pre-charge data signal low                      |          |

| 9   | PCDH   | С   | Capacitor for pre-charge data signal high                     |          |

| 10  | VCOML  | С   | Capacitor for VCOM low                                        |          |

| 11  | VCOMH  | С   | Capacitor for VCOM high                                       |          |

| 12  | AGND   |     | Analog ground                                                 |          |

| 13  | PVDD   | С   | Regulation capacitor for charge pump                          |          |

| 14  | AVDD   | С   | Regulation capacitor for analog voltage                       |          |

| 15  | CP1    | С   | Capacitor for charge pump                                     |          |

| 16  | CP2    | С   | Capacitor for charge pump                                     |          |

| 17  | PWM    | 0   | Power transistor gate signal for the boost converter          |          |

| 18  | FB     | Ι   | Main boost regulator feedback input                           |          |

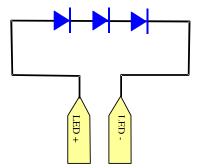

| 19  | LED-   |     | LED power: cathode                                            | Note 3-1 |

| 20  | LED+   | -   | LED power: anode                                              | NOLE 3-1 |

| 21  | NC     |     | No connection                                                 |          |

| 22  | GND    |     | Ground                                                        |          |

| 23  | VCC    | -   | Power supply                                                  |          |

| 24  | VD     | Ι   | Vertical sync input                                           |          |

| 25  | HD     | Ι   | Horizontal sync input                                         |          |

| 26  | DCLK   | Ι   | Clock signal, latch data onto line latches at the rising edge |          |

| 27  | DIN0   | I   | Data input                                                    |          |

| 28  | DIN1   | Ι   | Data input                                                    |          |

| 29  | DIN2   | Ι   | Data input                                                    |          |

| 30  | DIN3   | Ι   | Data input                                                    |          |

| 31  | DIN4   | Ι   | Data input                                                    |          |

| 32  | DIN5   | Ι   | Data input                                                    |          |

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

# TD025WHEB2

| 33 | DIN6   | Ι   | Data input                        |  |

|----|--------|-----|-----------------------------------|--|

| 34 | DIN7   | Ι   | Data input                        |  |

| 35 | SDA    | I/O | Serial interface data line        |  |

| 36 | SCL    | Ι   | Serial interface clock line       |  |

| 37 | SCEN   | Ι   | Serial interface chip enable line |  |

| 38 | SHDB   | I   | Sleep mode setting pin            |  |

| 39 | GRESTB | Ι   | Global reset pin                  |  |

Note 3-1: The figure below shows the connection of backlight LED.

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

# 4. ABSOLUTE MAXIMUM RATINGS

Ta = 25°C

| Item                       | Symbol           | MIN  | MAX             | Unit | Remark                                                        |

|----------------------------|------------------|------|-----------------|------|---------------------------------------------------------------|

| Power Supply Voltage       | V <sub>cc</sub>  | -0.5 | 4.5             | V    |                                                               |

| Input Signal Voltage       | V <sub>IN1</sub> | 0    | V <sub>cc</sub> | V    | VD, HD, DCLK,<br>DIN[0:7], SDA,<br>SCL, SCEN,<br>SHDB, GRESTB |

| Back Light Forward Current | I <sub>F</sub>   |      | 25              | mA   |                                                               |

| Operating Temperature      | T <sub>OPR</sub> | -10  | +60             | °C   |                                                               |

| Storage Temperature        | T <sub>STG</sub> | -30  | +80             | °C   |                                                               |

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

# 5. ELECTRICAL CHARACTERISTICS

5.1 Driving TFT LCD Panel

|                         |            |                 |           |     |           |      | GND=0V, Ta=25℃                       |

|-------------------------|------------|-----------------|-----------|-----|-----------|------|--------------------------------------|

| lte                     | em         | Symbol          | MIN       | TYP | MAX       | Unit | Remark                               |

| Power Supply Voltage    |            | $V_{CC}$        | 2.85      | 3.0 | 3.6       | V    | Note 5-1                             |

| Input Signal<br>Voltage | Low Level  | V <sub>IL</sub> | GND       | -   | 0.2x Vcc* | V    | VD, HD, DCLK,<br>DIN[0:7], SDA, SCL, |

|                         | High Level | V <sub>IH</sub> | 0.8x Vcc* | -   | Vcc*      | V    | SCEN, SHDB,<br>GRESTB                |

| PWM Output Voltage      |            | $V_{PWM}$       | 0         | -   | Vcc*      | V    |                                      |

| Feedback Voltage        |            | $V_{FB}$        | 0.55      | 0.6 | 0.65      | V    | Note 5-2                             |

| Panel Power Consumption |            | $W_{P}$         | -         | 50  | -         | mW   |                                      |

$Vcc^* = Vcc(TYP)$

Note 5-1: The Vcc power is provided for overall panel module supply voltage.

Note 5-2: DC/DC feedback control voltage

#### 5.2 Driving Backlight

Ta=25℃

| Item                        | Symbol         | MIN | TYP  | MAX | Unit | Remark   |

|-----------------------------|----------------|-----|------|-----|------|----------|

| Forward Current             | I <sub>F</sub> |     | 20   | 23  | mA   |          |

| Forward Current Voltage     | $V_{F}$        |     | 10.8 | 12  | V    | Note 5-3 |

| Backlight Power Consumption | $W_{BL}$       |     | 216  | 276 | mW   |          |

Note 5-3: Backlight driving circuit is recommended as the fix current circuit.

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

### 6. TIMING CHART

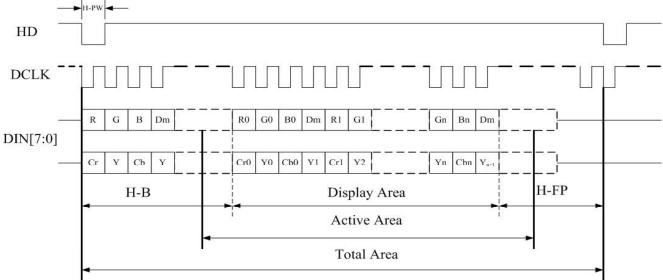

6.1 Serial RGB Dummy Mode and Serial YUV 4:2:2 Mode: Horizontal

# (1) YUV Mode: ITUR601-NTSC

| Item                      | Symbol       | MIN | TYP  | MAX | Unit |

|---------------------------|--------------|-----|------|-----|------|

| Dot Clock Frequency       | DCLK         | -   | 27   | -   | MHz  |

| Horizontal Display Active | Display Area | -   | 1440 | -   | DCLK |

| Horizontal Total Time     | Total Area   | -   | 1716 | -   | DCLK |

| HSYNC Pulse Width         | H-PW         | -   | 1    | -   | DCLK |

| Horizontal Back Porch     | H-B          | -   | 240  | -   | DCLK |

| Horizontal Front Porch    | H-FP         | -   | 36   | -   | DCLK |

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

#### (2) YUV Mode: ITUR601-PAL

| Item                      | Symbol       | MIN | TYP  | MAX | Unit |

|---------------------------|--------------|-----|------|-----|------|

| Dot Clock Frequency       | DCLK         | -   | 27   | -   | MHz  |

| Horizontal Display Active | Display Area | -   | 1440 | -   | DCLK |

| Horizontal Total Time     | Total Area   | -   | 1728 | -   | DCLK |

| HSYNC Pulse Width         | H-PW         | -   | 1    | -   | DCLK |

| Horizontal Back Porch     | H-B          | -   | 240  | -   | DCLK |

| Horizontal Front Porch    | H-FP         | -   | 48   | -   | DCLK |

#### (3) RGB Dummy Mode

| ltem                      |       | Symbol       | MIN | TYP   | MAX | Unit |

|---------------------------|-------|--------------|-----|-------|-----|------|

| Dot Clock Fre-            | QVGA  |              | -   | 25    | -   |      |

|                           | NTSC  | DCLK         | -   | 24.54 | -   | MHz  |

| quency                    | PAL   |              | -   | 24.38 | -   |      |

| Horizontal Display Active |       | Display Area | -   | 1280  | -   | DCLK |

| Horizontal Total T        | ime   | Total Area   | -   | 1560  | -   | DCLK |

| HSYNC Pulse Width         |       | H-PW         | -   | 1     | -   | DCLK |

| Horizontal Back Porch     |       | H-B          | -   | 240   | -   | DCLK |

| Horizontal Front F        | Porch | H-FP         | -   | 40    | -   | DCLK |

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

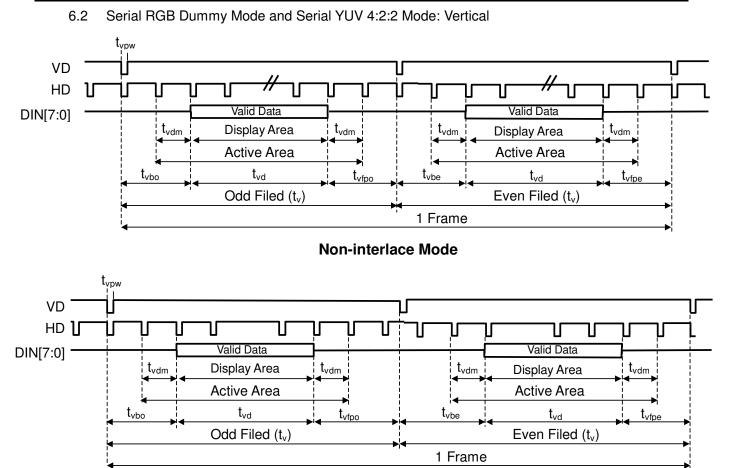

Interlace Mode

| Item               |            | Symbol            | MIN | TYP | MAX | Unit |

|--------------------|------------|-------------------|-----|-----|-----|------|

| Vertical Display   | Active     | t <sub>vd</sub>   | -   | 240 | -   | Line |

| Vertical Total Tin | ne         | t <sub>v</sub>    | -   | 262 | -   | Line |

| VSYNC Pulse Width  |            | t <sub>vpw</sub>  | 1   | 1   | -   | DCLK |

| Vertical Back      | Odd Field  | t <sub>vbo</sub>  | -   | 21  | -   | Line |

| Porch              | Even Field | t <sub>vbe</sub>  | -   | 21  | -   | Line |

| Vertical Front     | Odd Field  | t <sub>vfpo</sub> | -   | 1   | -   | Line |

| Porch              | Even Field | t <sub>vfpe</sub> | -   | 1   | -   | Line |

| Vertical Dummy     |            | t <sub>vdm</sub>  | -   | 0   | -   | Line |

#### (1) Non-Interlace Mode: NTSC/QVGA

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

#### (2) Non-Interlace Mode: PAL

| Item               |            | Symbol            | MIN | TYP | MAX | Unit |

|--------------------|------------|-------------------|-----|-----|-----|------|

| Vertical Display A | Active     | t <sub>vd</sub>   | -   | 288 | -   | Line |

| Vertical Total Tim | е          | t <sub>v</sub>    | -   | 312 | -   | Line |

| VSYNC Pulse Width  |            | t <sub>vpw</sub>  | 1   | 1   | -   | DCLK |

| Vertical Back      | Odd Field  | t <sub>vbo</sub>  | -   | 24  | -   | Line |

| Porch              | Even Field | $t_{vbe}$         | -   | 24  | -   | Line |

| Vertical Front     | Odd Field  | t <sub>vfpo</sub> | -   | 0   | -   | Line |

| Porch              | Even Field | $t_{vfpe}$        | -   | 0   | -   | Line |

| Vertical Dummy     |            | t <sub>vdm</sub>  | -   | 0   | -   | Line |

#### (3) Interlace Mode: NTSC/QVGA

| Item               |            | Symbol            | MIN | TYP   | MAX | Unit |

|--------------------|------------|-------------------|-----|-------|-----|------|

| Vertical Display A | ctive      | $t_{vd}$          | -   | 240   | -   | Line |

| Vertical Total Tim | е          | t <sub>v</sub>    | -   | 262.5 | -   | Line |

| VSYNC Pulse Width  |            | t <sub>vpw</sub>  | 1   | 1     | -   | DCLK |

| Vertical Back      | Odd Field  | $t_{vbo}$         | -   | 21    | -   | Line |

| Porch              | Even Field | $t_{vbe}$         | -   | 21.5  | -   | Line |

| Vertical Front     | Odd Field  | t <sub>vfpo</sub> | -   | 1.5   | -   | Line |

| Porch              | Even Field | t <sub>vfpe</sub> | -   | 1     | -   | Line |

| Vertical Dummy     |            | t <sub>vdm</sub>  | -   | 0     | -   | Line |

#### (4) Interlace Mode: PAL

| Item               |            | Symbol            | MIN | TYP   | MAX | Unit |

|--------------------|------------|-------------------|-----|-------|-----|------|

| Vertical Display A | Active     | t <sub>vd</sub>   | -   | 288   | -   | Line |

| Vertical Total Tim | ie         | t <sub>v</sub>    | -   | 312.5 | -   | Line |

| VSYNC Pulse W      | ïdth       | t <sub>vpw</sub>  | 1   | 1     | -   | DCLK |

| Vertical Back      | Odd Field  | t <sub>vbo</sub>  | -   | 24    | -   | Line |

| Porch              | Even Field | $t_{vbe}$         | -   | 24.5  | -   | Line |

| Vertical Front     | Odd Field  | t <sub>vfpo</sub> | -   | 0.5   | -   | Line |

| Porch              | Even Field | t <sub>vfpe</sub> | -   | 0     | -   | Line |

| Vertical Dummy     |            | t <sub>vdm</sub>  | -   | 0     | -   | Line |

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

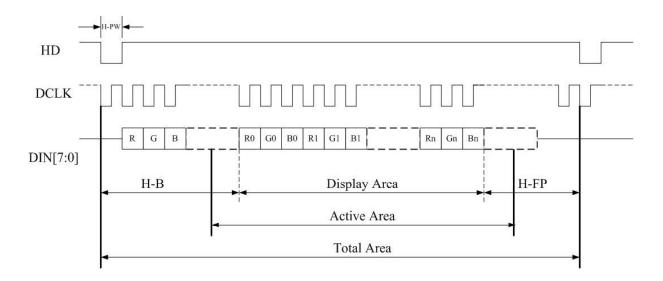

#### 6.3 Through Mode: Horizontal

| Item                      | Symbol       | MIN | TYP   | MAX | Unit |

|---------------------------|--------------|-----|-------|-----|------|

| Dot Clock Period          | DCLK         |     | 76.16 |     | ns   |

| Horizontal Display Active | Display Area | -   | 640   | -   | DCLK |

| Horizontal Total Time     | Total Area   | -   | 820   | -   | DCLK |

| HSYNC Pulse Width         | H-PW         | -   | 1     | -   | DCLK |

| Horizontal Back Porch     | H-B          | -   | 117   | -   | DCLK |

| Horizontal Front Porch    | H-FP         | -   | 63    | -   | DCLK |

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

TD025WHEB2

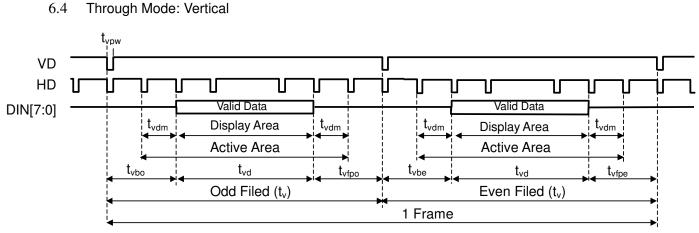

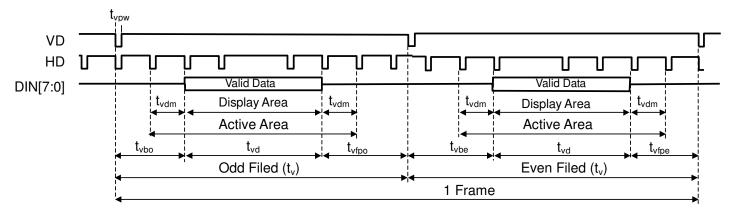

Non-Interlace Mode

Interlace Mode

| Item               |            | Symbol            | MIN | TYP | MAX | Unit |

|--------------------|------------|-------------------|-----|-----|-----|------|

| Vertical Display A | Active     | t <sub>vd</sub>   | -   | 240 | -   | Line |

| Vertical Total Tim | e          | t <sub>v</sub>    | -   | 262 | -   | Line |

| VSYNC Pulse Width  |            | t <sub>vpw</sub>  | 1   | 1   | -   | DCLK |

| Vertical Back      | Odd Field  | t <sub>vbo</sub>  | -   | 14  | -   | Line |

| Porch              | Even Field | $t_{vbe}$         | -   | 14  | -   | Line |

| Vertical Front     | Odd Field  | t <sub>vfpo</sub> | -   | 8   | -   | Line |

| Porch              | Even Field | t <sub>vfpe</sub> | -   | 8   | -   | Line |

| Vertical Dummy     |            | t <sub>vdm</sub>  | -   | 0   | -   | Line |

(1) Non-Interlace Mode

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

#### (2) Interlace Mode

| Item               |            | Symbol            | MIN | TYP   | MAX | Unit |

|--------------------|------------|-------------------|-----|-------|-----|------|

| Vertical Display A | Active     | t <sub>vd</sub>   | -   | 240   | -   | Line |

| Vertical Total Tim | e          | t <sub>v</sub>    | -   | 262.5 | -   | Line |

| VSYNC Pulse W      | idth       | t <sub>vpw</sub>  | 1   | 1     | -   | DCLK |

| Vertical Back      | Odd Field  | t <sub>vbo</sub>  | -   | 14    | -   | Line |

| Porch              | Even Field | $t_{vbe}$         | -   | 14.5  | -   | Line |

| Vertical Front     | Odd Field  | t <sub>vfpo</sub> | -   | 8.5   | -   | Line |

| Porch              | Even Field | $t_{vfpe}$        | -   | 8     |     | Line |

| Vertical Dummy     |            | t <sub>vdm</sub>  | -   | 0     | -   | Line |

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

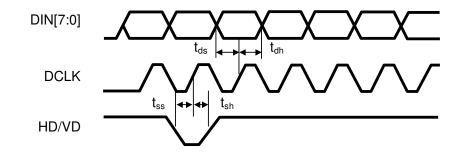

#### 6.5 Setup Time and Hold Time

| Item                      | Symbol          | MIN | TYP | MAX | Unit |

|---------------------------|-----------------|-----|-----|-----|------|

| DCLK Duty Ratio           | -               | 40  | -   | 60  | %    |

| Data Setup Time           | t <sub>ds</sub> | 12  | -   | -   | ns   |

| Data Hold Time            | t <sub>dh</sub> | 12  | -   | -   | ns   |

| Control Signal Setup Time | t <sub>ss</sub> | 12  | -   | -   | ns   |

| Control Signal Hold Time  | t <sub>sh</sub> | 12  | -   | -   | ns   |

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

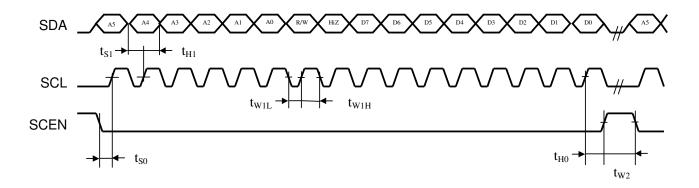

#### 6.6 Serial Interface Timing

| Parameter       | Symbol           | Condition        | MIN | TYP | MAX | Unit |

|-----------------|------------------|------------------|-----|-----|-----|------|

| Data Setup Time | t <sub>so</sub>  | SCEN to SCL      | 150 | -   | -   | ns   |

| Data Setup Time | t <sub>S1</sub>  | SDA to SCL       | 150 | -   | -   | ns   |

|                 |                  | SCEN to SCL      | 150 | -   | -   | ns   |

| Data Hold Time  | t <sub>H1</sub>  | SDA to SCL       | 150 | -   | -   | ns   |

|                 | t <sub>W1L</sub> | SCL pulse width  | 160 | -   | -   | ns   |

| Pulse width     | t <sub>w1H</sub> | SCL pulse width  | 160 | -   | -   | ns   |

|                 | t <sub>W2</sub>  | SCEN pulse width | 1.0 | -   | -   | us   |

| Clock Duty      | -                | SCL duty ratio   | 40  | 50  | 60  | %    |

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

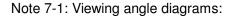

# 7. OPTICAL CHARACTERISTICS

7.1 Optical Specification

|                                  |         |                |           |      |      |      |                   | <b>Ta=25°</b> ℃ |

|----------------------------------|---------|----------------|-----------|------|------|------|-------------------|-----------------|

| Item                             |         | Symbol         | Condition | MIN  | TYP  | MAX  | Unit              | Remarks         |

|                                  |         | θ11            |           | 40   | 50   | -    |                   |                 |

| Viewing Angles                   |         | θ12            | CR ≥ 10   | 40   | 50   | -    | Degree            | Note 7-1        |

| viewing Angles                   |         | <b>⊖21</b>     | 0n 2 10   | 25   | 35   | -    | Degree            | Note 7-1        |

|                                  |         | <b>⊖22</b>     |           | 45   | 55   | -    |                   |                 |

| Contrast Ratio                   |         | CR             | ⊖=0°      | 300  | 400  | -    |                   | Note 7-2        |

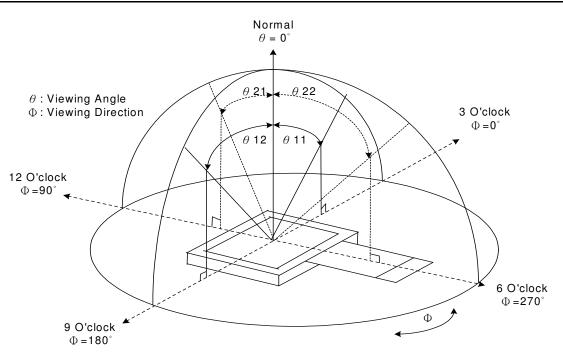

| Response Time                    | Rising  | Tr             | ⊖=0*      | 13   | 25   | 20   | ms                | Note 7-3        |

| nesponse nine                    | Falling | Tf             | -         | 22   | 45   | 25   | 1115              | NOLE 7-5        |

| Luminance (I <sub>F</sub> =20mA) |         | L              | 0.26      | 300  | 350  | -    | cd/m <sup>2</sup> | Note 7-4        |

| Chromaticity                     | White   | x <sub>w</sub> | 0.20      | 0.31 | 0.36 | 0.36 |                   | Note 7-5        |

|                                  | vville  | Уw             | 0.20      | 0.33 | 0.38 | 0.39 |                   | NOLE 7-5        |

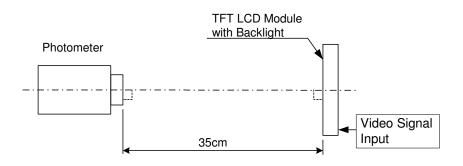

7.2 Basic Measure Conditions

(1) Driving voltage

VCC= 3 V

- (2) Ambient Temperature: Ta=25°C

- (3) Testing Point: Measure in the display center point and the test angle $\ominus = 0^{\circ}$

- (4) LED Current:  $I_F=20mA$ .

- (5) Testing Facility

Environmental illumination:  $\leq$  1 Lux

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

Note 7-2: Contrast Ratio:

Contrast ratio is measured in optimum common electrode voltage.

CR = Luminance with white image

Luminance with black image

Note 7-3: Definition of response time:

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

Note 7-4: Luminance:

Test Point: Display Center

Note 7-5: Chromaticity: The same test condition as Note 7-4.

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

#### 8. RELIABILITY

| No | Test Item                                                     | Condition                                      |  |  |

|----|---------------------------------------------------------------|------------------------------------------------|--|--|

| 1  | High Temperature Operation                                    | Ta=+60℃, 240hrs                                |  |  |

| 2  | High Temperature & High Humidity Operation                    | Ta=+40℃, 95% RH, 240hrs                        |  |  |

| 3  | Low Temperature Operation                                     | Ta=-10℃, 240hrs                                |  |  |

| 4  | High Temperature Storage (non-operation)                      | Ta=+80℃, 240hrs                                |  |  |

| 5  | Low Temperature Storage (non-operation)                       | Ta=-30℃ , 240hrs                               |  |  |

| 6  | Thermal Sheek (non-operation)                                 | -30°C                                          |  |  |

| 0  | Thermal Shock (non-operation)                                 | 30 min   30 min                                |  |  |

|    | Pasistanas to Statis Electrisity Discharge                    | C=200pF, R=0Ω;                                 |  |  |

| 7  | Resistance to Static Electricity Discharge<br>(non-operation) | Discharge: ±150V                               |  |  |

|    |                                                               | 3 times / Terminal                             |  |  |

|    |                                                               | C=150pF, R=330Ω;                               |  |  |

| 8  | Surface Discharge (non-operation)                             | Discharge: Air: ±15kV; Contact: ±8kV           |  |  |

|    |                                                               | 5 times / Point; 5 Points / Panel              |  |  |

|    |                                                               | Frequency: 10~55Hz; Amplitude: 1.5mm           |  |  |

| 9  | Vibration (non-operation)                                     | Sweep Time: 11min                              |  |  |

|    |                                                               | Test Time: 2 hrs for each direction of X, Y, Z |  |  |

| 10 | Shock (non-operation)                                         | Acceleration: 100G; Period: 6ms                |  |  |

| 10 |                                                               | Directions: ±X, ±Y, ±Z; Cycles: Twice          |  |  |

Ta: Ambient Temperature

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

#### 9. HANDLING CAUTIONS

9.1 ESD (Electrical Static Discharge) Strategy

ESD will cause serious damage of the panel, ESD strategy is very important in handling. Following items are the recommend ESD strategy

- (1) In handling LCD panel, please wear non-charged material gloves. And the conduction ring connect wrist to the earth and the conducting shoes to the earth is necessary.

- (2) The machine and working table for the panel should have ESD prohibition strategy.

- (3) In handling the panel, ionize flowing decrease the charge in the environment is necessary.

- (4) In the process of assembly the module, shield case should connect to the ground.

#### 9.2 Environment

- (1) Working environment of the panel should in the clean room.

- (2) The front polarizer is easy damaged, handle it carefully and do not scratch it by sharp material.

- (3) Panel has polarizer protective film in the surface please remove the protection film of polarizer slowly with ionized air to prevent the electrostatic discharge.

#### 9.3 Others

- (1) Turn off the power supply before connecting and disconnecting signal input cable.

- (2) The connection area of FPC and panel is very weak, do not handle panel only by FPC or bend FPC.

- (3) Water drop on the surface or condensation as panel power on will corrode panel electrode.

- (4) As the packing bag open, watch out the environment of the panel storage. High temperature and high humidity environment is prohibited.

- (5) When the TFT LCD module is broken, please watch out whether liquid crystal leaks out or not. If your hand touches liquid crystal, wash your hand cleanly by water and soap as soon as possible.

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

# **10. MECHANICAL DRAWING**

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

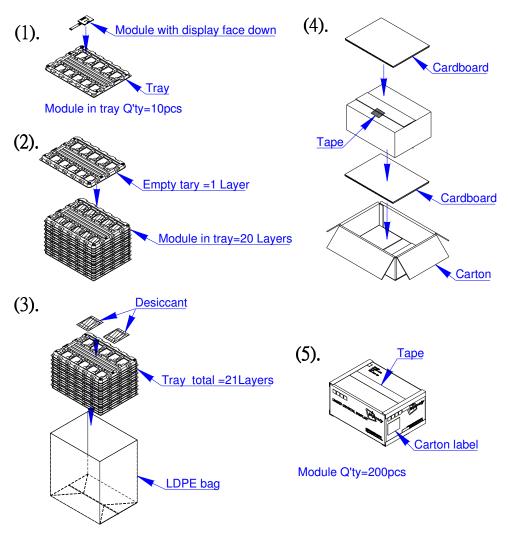

11. Packing Drawing

- 2.5" module (TD025WHEB2) delivery packing method

- (1). Module packed into tray cavity (with Module display face down).

- (2). Tray stacking with 20 layers and with 1 empty tray above the stacking tray unit.2pcs desiccant put above the empty tray

- (3). Stacking tray unit put into the LDPE bag and fix by adhesive tape.

- (4). Put 1pc cardboard inside the carton bottom, then pack the package unit into the carton. put 1pc cardboard above the package unit.

- (5). Carton tapping with adhesive tape.

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.