#### 1. FEATURES

The 3.0" LCD module is the active matrix color TFT LCD module. LTPS (Low Temperature Poly Silicon) TFT technology is applied with vertical and horizontal drivers built on the panel.

Both of horizontal and vertical scan are reversible and controlled by the serial interface commands. The product is designed for the requirement of the green product, and the specification complies with Toppoly's "Green Product Chemical Substance Specification Standard Hand Book".

#### 2. GENERAL SPECIFICATIONS

| Item                          | Description        | Unit |

|-------------------------------|--------------------|------|

| Display Size (Diagonal)       | 3.0                | Inch |

| Aspect ratio                  | 4:3                | -    |

| Display Type                  | Transmissive       | •    |

| Active Area (HxV)             | 60.03×45           | mm   |

| Number of Dots (HxV)          | 960 x 240          | Dot  |

| Dot Pitch (HxV)               | 0.0625 x 0.1875    | mm   |

| Color Arrangement             | RGB Delta          | -    |

| Color Numbers                 | 16Million          | -    |

| NTSC                          | 40                 | %    |

| Outline Dimension (H x V x T) | 70.5 x 52.2 x 3.97 | mm   |

| Weight                        | 27.8               | G    |

<sup>\*</sup>Exclude FPC and protrusions.

Page: 4/22

## 3. INPUT/OUTPUT TERMINALS

### 3.1TFT LCD Panel

Recommend connector:

Compatible with HRS FH26-45S-0.3SHW

| Pin | Symbol | 1/0 | Description                                              | Remark   |

|-----|--------|-----|----------------------------------------------------------|----------|

| 1   | CP3    | С   | Capacitor for power setting                              |          |

| :2  | CP4    | С   | Capacitor for power setting                              |          |

| 3   | CP5    | С   | Capacitor for charge pump                                |          |

| 4   | CP6    | С   | Capacitor for charge pump                                |          |

| 5   | CP7    | С   | Capacitor for charge pump                                |          |

| 6   | CP8    | С   | Capacitor for charge pump                                |          |

| 7   | DUMMY  |     | Dummy                                                    |          |

| В   | DUMMY  |     | Dummy                                                    |          |

| 9   | PCD    | С   | Capacitor for pre-charge data signal high                |          |

| 10  | VCOML  | С   | Capacitor for VCOM low                                   |          |

| 1:1 | VCOMH  | С   | Capacitor for VCOM high                                  |          |

| 12  | AGND   |     | Analog ground                                            |          |

| 13  | DUMMY  |     | Dummy                                                    |          |

| 14  | AVDD   | С   | Regulation capacitor for analog voltage                  |          |

| 15  | CP1    | С   | Capacitor for charge pump                                |          |

| 16  | GP2    | С   | Capacitor for charge pump                                |          |

| 17  | PWM    | 0   | Power transistor gate signal for the boost converter     |          |

| 18  | FB     | 1   | Main boost regulator feedback input.                     |          |

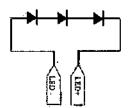

| 19  | LED-   |     | LED power: cathode                                       | Note 3-1 |

| 20  | LED-   |     | LED power: cathode                                       | Note 3-1 |

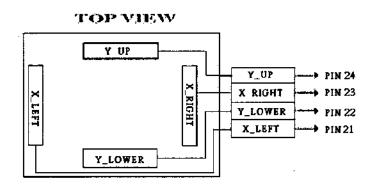

| 21  | XL     | 0   | T/P terminal (X-Right) Note:                             |          |

| 22  | YL     | 0   | T/P terminal (Y-Upper) Note 3                            |          |

| 23  | XR     | 0   | T/P terminal (X-Left)                                    | Note 3-2 |

| 24  | YU     | 0   | T/P terminal (Y-Lower)                                   | Note 3-2 |

| 25  | DUMMY  |     | Dummy                                                    |          |

| 26  | LED+   |     | LED power: anode                                         | Note 3-1 |

| 27  | LED+   |     | LED power: anode Note 3-1                                |          |

| 28  | GND    |     | Ground                                                   |          |

| 29  | VCC    |     | Power supply for digital circuit and charge pump circuit |          |

| 30  | VSYNC  | I   | Vertical sync input. Negative polarity                   |          |

| 31  | HSYNC  | I   | Horizontal sync input. Negative polarity                 |          |

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

Page: 5/22

| 32 | DCLK  | ı   | Clock signal, latch data onto line latches at the rising edge |         |

|----|-------|-----|---------------------------------------------------------------|---------|

| 33 | DIN0  | ı   | Data input                                                    |         |

| 34 | DIN1  | 1   | Data input                                                    |         |

| 35 | DIN2  | ı   | Data input                                                    |         |

| 36 | DIN3  | 1   | Data input                                                    |         |

| 37 | DIN4  | 1   | Data input                                                    |         |

| 38 | DIN5  | ı   | Data input                                                    |         |

| 39 | DIN6  | I   | Data input                                                    |         |

| 40 | DIN7  | I   | Data input                                                    |         |

| 41 | SDA   | 1/0 | Serial interface data line                                    |         |

| 42 | SCL   | L   | Serial interface clock line                                   |         |

| 43 | SCEN  | 1   | Serial interface chip enable line                             |         |

| 44 | SHDB  | Ī   | Shutdown input                                                | Note 2: |

| 45 | GREST | ı   | System reset pin                                              |         |

I: Input O: Output P: Power C: Capacitor D: Dummy I/O: Input/Output

Note 2: SHDB

Pull High: Sleep mode is controlled by register setting. (address: 0x04)

Pull Low: Panel is in sleep mode

Note 3-1: The figure below shows the connection of backlight LED.

Note 3-2: The figure below shows the connection of Touch panel. (top view)

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

Page: 6/22

# FPC is 45 pin (include touch panel interface):

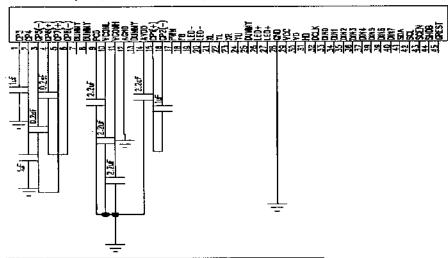

| Application side | Capacitance<br>(F) | Rated voltage (V) |  |

|------------------|--------------------|-------------------|--|

| CP1              | 1u                 | 16                |  |

| CP2              | Iu                 |                   |  |

| CP3              | 1u                 | 16                |  |

| CP4              | 1u                 | 25                |  |

| CP5              | 0. <b>2</b> u      | 25                |  |

| CP7              | 0.20               |                   |  |

| CP6              | 0.2u               | 25                |  |

| CP8              | 0.20               | 25                |  |

| AVDD             | 2.2u               | 16 ·              |  |

| PCD              | 2.2u               | 16                |  |

| VCOMH            | 2.2u               | 16                |  |

| VCOML            | 2.2u               | 16                |  |

CP1→CP2(1 uF) capacitor suggest using X5R dielectric.

Page: 7/22

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

#### 9 HANDLING CAUTIONS

### 9.1 ESD (Electrical Static Discharge) Strategy

ESD will cause serious damage of the panel, ESD strategy is very important in handling. Following items are the recommend ESD strategy

- (1) In handling LCD panel, please wear non-charged material gloves. And the conduction ring connect wrist to the earth and the conducting shoes to the earth is necessary.

- (2) The machine and working table for the panel should have ESD prohibition strategy.

- (3) In handling the panel, ionize flowing decrease the charge in the environment is necessary.

- (4) In the process of assembly the module, shield case should connect to the ground.

#### 9.2 Environment

- (1) Working environment of the panel should in the clean room.

- (2) The front polarizer is easy damaged, handle it carefully and do not scratch it by sharp material.

- (3) Panel has polarizer protective film in the surface please remove the protection film of polarizer slowly with ionized air to prevent the electrostatic discharge.

#### 9.3 Touch panel

- (1) The front touch panel is vulnerable to heavy weight, so any input must be done by special stylus or by a finger. Do not put any heavy stuff on it.

- (2) When any dust or stain is observed on a film surface, clean it using a lens cleaner for glasses or something similar.

#### 9.4 Others

- (1) Turn off the power supply before connecting and disconnecting signal input cable.

- (2) The connection area of FPC and panel is very weak, do not handle panel only by FPC or bend FPC.

- (3) Water drop on the surface or condensation as panel power on will corrode panel electrode.

- (4) As the packing bag open, watch out the environment of the panel storage. High temperature and high humidity environment is prohibited.

- (5) When the TFT LCD module is broken, please watch out whether liquid crystal leaks out or not. If your hand touches liquid crystal, wash your hand cleanly by water and soap as soon as possible.

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

Page: 22/22

### 10 Application Note

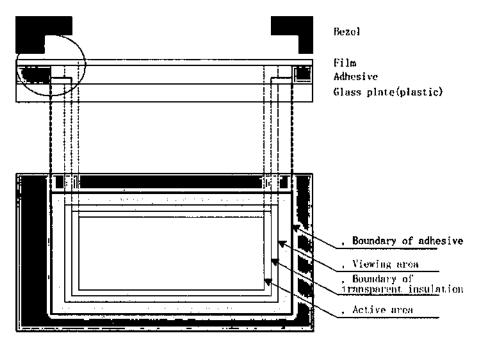

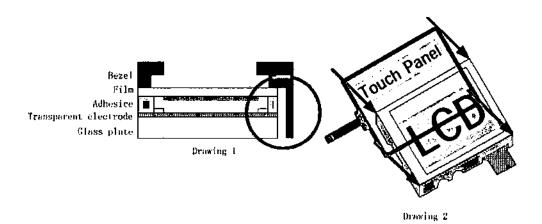

- 10.1 Design notes on touch panel

- (1) Explanation of each boundary of touch panel

- A. Boundary of Double-sided adhesive

- a. Electrically detectable within this zone.

When holding the touch panel by housing, it needs to be held at outside of this zone.

- b. Film is supported by double-sided adhesive tape.

- B. Viewing area

- a. Cosmetic inspection to be done for this area.

This area is set as inside of boundary of double-sided adhesive with tolerance.

- C. Boundary of transparent insulation

- a. Purpose is to "Help" to secure insulation.

- b. Electrical insulation on this area is not guaranteed.

- c. We do recommend not to hold this area by something like housing or gasket.

- D. Active area

- a. This area is where the performance is guaranteed.

This area set as some distance inside from the boundary area of double-sided adhesive tape since its neighboring area is less durable to writing friction.

- b. Please refer to the attached module drawing for the bezel opening and window size design.

There is some possibility to damage ITO

No Damage to ITO

Page: 23/22

- (2) Housing and touch panel

- a. Please have clearance between the side of touch panel, and any conductive material such as metal frame.(drawing.1) Transparent electrode exists on glass of touch panel from end to end.

- b. It is recommended to fix a touch panel on the LCD module chassis rather than the touch panel housing. Clinging at conductive material and side of touch panel might cause malfunction.

Page: 24/22

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

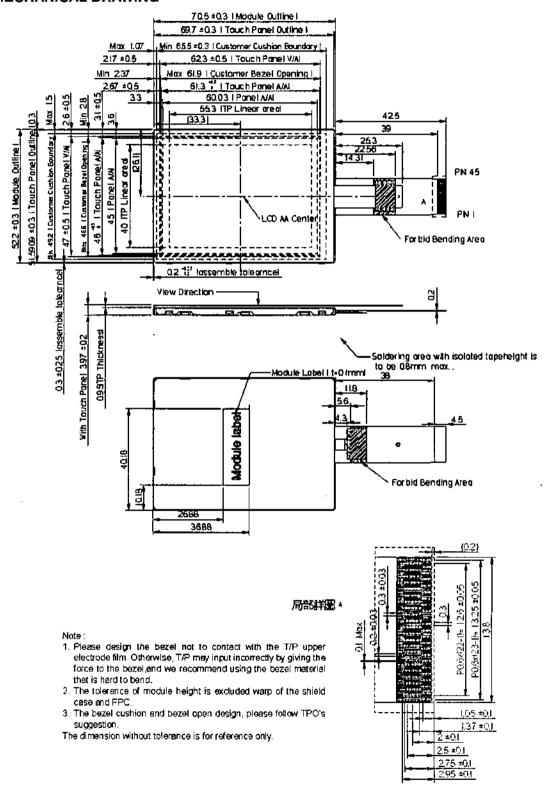

### 11 MECHANICAL DRAWING

The information contained herein is the exclusive property of toppoly Optoelectronics corporation, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of toppoly Optoelectronics corporation.

Page: 25/22